# Efficient Error Correction Codes for Multiple-cell Upset in SRAM

A. Kaviya, G.Sivapriya

A. Assistant Professor, Department of Electronics and Communication Engineering, B. M.Kumarasamy College of Engineering, Thalavapalayam, Karur, Tamil Nadu

Article Info Volume 82

Page Number: 330 - 336 Publication Issue: January-February 2020

Article History

Article Received: 14 March 2019

Revised: 27 May 2019 Accepted: 16 October 2019 Publication: 02 January 2020

#### Abstract

Currently, faults suffered through SRAM reminiscence systems have increased because of the aggressive CMOS integration density. Thus, the probability of occurrence of single-mobile upsets (SCUs) or a couple of-cell upsets (MCUs) augments. One of the primary causes of MCUs in space packages is cosmic radiation. A not unusual solution is the use of blunders correction codes (ECCs). Modern superscalar processors enforce sign up renaming using either random get admission to memory (RAM) tables. The design of those systems ought to address both get admission to time and misprediction restoration penalty. Although direct-mapped RAMs offer faster get right of entry to times, RAMs are more suitable to avoid recovery consequences. The benefits of the hybrid design stem from principal resources. On the one hand, the processors exertion in a no speculative mode in the not unusual case, as a result RAM invalidations are unusual. On the other hand, often done commands (e.g., loops) most effective utilize a minute subset of the architected check in report, as a result just a few RAM updates suffices to get better the steady country. Thus, a discount of the Space complexity does now not harm performance, however lowers its strength intake, vicinity, and access time. Also, those new codes preserve, or even improve, reminiscence errors coverage with respect to Matrix codes.

Keywords: Small Finance Banks, Financial Inclusion, NBFCs, Information and

Communication Technology, Micro Credit, Reserve Bank of India.

## I. INTRODUCTION

Modern high performance processors implement out-of-order and speculative execution to increase performance through efficient register renaming. Many mechanisms are devised to increase the amount of instructions executing concurrently. The register renaming techniques are used to overcome Write after Write and Write after Read data hazards.

Register renaming distinguishes two sorts of registers: Logical registers and Physical registers. Logical registers are utilized by the compiler and Physical registers are honestly carried out within the machine. The numbers of physical registers are large than the wide variety of logical registers. When a guidance that produces the decoded outcomes, there renaming logic allocates a free physical registers. The logical vacation spot registers is said to be mapped to that physical registers. Subsequent records

based instructions rename their source registers to get admission to this physical; registers. The sign in renaming circuitry offers with sign in mapping

desk healing whilst mispeculation takes place. Highly accessed renaming systems are important, due to their excessive electricity density.

Register renaming is carried out by Random get entry to reminiscence (RAM) and content addressable memory (CAM). Industries don't display the important trend, they makes use of the each procedures. The contemporary mappings are obtained by using renaming the logical supply sign up the usage of its identifier. The mapping is completed quicker and extra efficaciously with RAM shape since the source sign in is at once listed, while the comparing is achieved against all present day mappings.

The approach is used because the test points permit for

quick restoration of the perfect mappings after speculation in both RAM and CAM. When the wide variety of test points will increase CAM provide quicker and green take a look at pointing than RAM takes a look at pointing.

In this paper, an innovative proposal that tries to take the first-rate of each implementation, this is faster register renaming, faster sign in allocation and rapid healing. The hybrid method we introduced makes use of both RAM and CAM. When a preparation is accomplished, if the direction execution is accurate the RAM offer mappings and performing as a cache of the CAM.

It is possibly so called cache CAM; here the RAM is performing because the cache reminiscence. The CAM is taking a look at pointed whenever a branch is decoded permitting quick mispeculation restoration, when invalidation is unusual.

The done commands (e.g.: loops) makes use of a small separation of that check in file, hence lone some RAM updates had to get better the constant state. Thus a reduction of CAM complexity does not hurt performance however decrease its energy intake, vicinity and get entry to time.

## **II.RELATED WORK**

## A. RAM Approach

The following example illustrates how an average RAM-primarily based method works. A code snippet which includes nine commands, whose 4 vacation spot registers (r5-r8) are renamed interested in six bodily registers ( $\rho 11-\rho 16$ ) is revealed in Fig. 1-a. The proposed RAM stuffing on the instant coaching I reaches the rename stage are shown in Fig. 1-b. At this position, its basis register are replaced to  $\rho 11$  and  $\rho 12$ . accumulation, a free bodily check in  $(\rho 16)$  is allotted to r7. To allocate an unfastened physical sign up, RAM methods use a free index queue (FRQ). After I am renamed, subsequent instructions having a data confidence on r7 could be renamed to p16. The straight mapped remembrance lets in the mappings to be swiftly accomplished while taking over a small place. Later, on the dedicate degree; physical registers are launched with the aid of placing their identifiers returned into the FRQ. The best approach for misspeculation healing is composed in ready until the mispredicted department reaches the reorder buffer (ROB) head [improve at entrust, see Fig. 1]. As ROB entries comprise the previous mapping for the vacation spot check in, the correct RAM state may be restored by way of scanning the ROB as soon as the offending practice reaches the ROB head get better at dedicate incurs a penalty with principal components: 1) the time onwards due to the fact the misprediction is identified until the mispredicted education reaches the dedicate degree and a pair of the point in time essential to reinstate the accurate mappings. The 2d element can be decreased the use of RAM's, a front-give up RAM (F-RAM), and a retreat RAM (R-RAM).

## **B.CAM Techniques**

CAM have as numerous rows because the variety of to be had bodily registers. Every row keeps statistics for renaming, improvement, and sign in allotment, as exposed in Fig. 2. The primary attribute suggests the mapped rational sign in, while the second columns specify whether or not this mapping is presently lively otherwise no longer.

Allow us expect an easy plan in which the record mappings be test pointed every instance a department coaching is decoded. A passage in a proposed CAM desk having the present day mappings and situate of subdivision limit points is verified inside Fig. 2. That desk consists of the renaming records just like the code on the time education I locates the rename phase. From source starting registers r5 and r6 of practice I are renamed to p11 and p12, in that order, objective check in r7, formerly map to  $\rho$ 13, is remapped to  $\rho$ 16, which is acquired through using the use of manner of a precedence encoder (PE) linked toward the unfastened attribute. Then, this fetching map is updated in the RAM equivalent input entries (logical Boolean value will join up and contemporary map fetching) of the proposed CAM. Concurrently, the contemporary-day mapping get right input entry to of p13 is reorganizing. Lastly, department test point columns cp H, cpF, and cp A hold the reproduction of the contemporary mapping attribute at the instant the equivalent department (i.e., H, F, and A) is decode. Depending at the accomplishment, test points may exist finished indiscriminately or selectively.

Creating a test point genuinely consists of replication the current mapping attribute.

Concerning sign up allotment, a bodily record is thought toward exist loose whilst it's in progress mapping 0's and 1's bit is obvious and it's not current in some test point. The instance,  $\rho$ 11,  $\rho$ 12,  $\rho$ 15, and  $\rho$ 16 are presently mapped, therefore they cannot be released. Although p13 is, but, now not currently mapped, it cannot be launched until each branches F and H are determined and recounted to be non-speculative, as  $\rho 13$  appears in test points  $c\rho F$ and cp H. This is likewise the case of p14 in test point cpF .As a final point, p17 is free since it's miles neither presently map nor gift in some test point. Liberated registers may be present obtaining through manner of without a doubt NOR-ing the modern-day map with the department test points bits. As coping with numerous test points, the in progress mapping and branch test points columns may subsist prepared as a rounded row following utility order, in which the cutting-edge-day mapping is situated on the extremity, with the relaxation of the entry department consist of the test points. This accomplishment lets in used for a discount of equally the temporal penalty and energy utilization.

The CAM restoration prompt while bough F is determined since mispredicted, simply with the aid of approach of updating the extension indicator, the test point cpF attribute will become the modern-day map, and the map of r7 commencing  $\rho 13$  to  $\rho 16$  is incomplete. This is as well the case of r8, it truly is map to  $\rho 14$  once more. In adding together,  $\rho 15$  and  $\rho 16$  are launched, due to the reality they prevent being allocated via the present day map or some other test point. Observe that the small test points (i.e., cpF & cpH) are unnecessary and great aged test points are stored (i.e., cp A).

## III. PROPOSED WORK

The Fusion RAM CAM system uses tables: 1) CAM which contains full of sign up fetch mappings updated and 2) RAM which performing because an accumulation of the proposed CAM contains a separation of its renaming records. The proposed CAM table may be listed each at once with the aid of a bodily check in and associatively by way of the use of a logical sign up, as the RAM is indexed with means of a reasonable check in. A RAM get admission to within the hybrid scheme also can or might

not include a legitimate reproduction of the present day mapping, as indicated through an extra legitimate bit/get right of entry to. Record renaming is completed with the resource of definitely gaining access to the RAM, at the equal time as legitimate entries are hit. If an unfounded get right of entrance to be access, a RAM leave out is supposed to rise up and the proposed CAM is used to recover the present day fetch mapping. Consequently, the CAM is not seemed up in full of renaming cycles; however just ahead RAM misses, taking into account a lower range of CAM study/write ports in assessment with an ordinary existing CAM accomplishment.

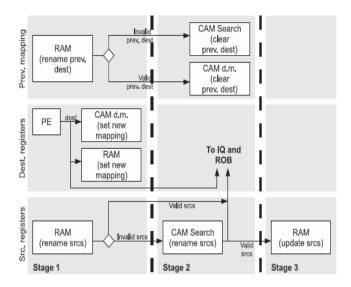

The existing over hypothesis, the entire RAM stuffing invalidating. Following recuperation, is cutting-edge-day mappings be simplest obtainable inside the CAM, since of the reality all RAM input entries are unacceptable. Succeeding renaming of foundation register will motive RAM miss, and the CAM may be appeared as much as collect the mappings. Mutually CAM lookups and novel sign up partition will motive the proposed RAM to be increasingly updated and fast decreasing the RAM fail to notice the fee. Permit us have a look at how the preceding effective example behave on the hybrid RAM-CAM. As commands reaches the rename stage. vacation spot registers are fetched to the novel substantial registers and the novel fetching is record every inside the proposed RAM and the proposed CAM. Behind renaming the practice I, proposed stuffing of RAM and content address tables. The block diagram show the proposed fig. Three is row wise separated in 3 sections are explained below.

# A. Clearing Previous Target Mappings

Proposed CAM input entries consequent to preceding

Vacation spot mappings are empty. In the primary degree, all preceding excursion spot mappings are appeared up within the RAM. For the ones legitimate entries, substantial join up identifiers are received, which can be after that used within the subsequent period to right now index key of the CAM and clean the contemporary fetching map input entries. The opposite, invalid RAM input entries reason preceding fetch the mappings to be associatively empty in the CAM.

Fig 1.Block diagram of the fusion RAM–CAM renaming steps.

## **B.** Target Register Renaming

Liberated bodily register are map to the purpose registers. The PE affords substantial check in identifiers from a hard and fast of loose entries within the proposed CAM. These recognizers are used to immediately index key of the CAM and position the original table fetch mappings. Novel mappings are besides bring up to date in the RAM, that's listed by the identifiers of the vacation spot rational registers.

## C. Source Register Renaming

For each deliver sign in, the related map material record identifier is received. In the number one degree, the RAM is access. Happening successful, mappings are obtainable right absent Or else, an associative CAM seek is finished in the 2nd degree. Lastly, the ones mappings repossess from the CAM are simplified in the RAM on the 1/3 period. This closing level be non-compulsory and could boom the RAM complication. However, it could offer overall presentation plus strength blessings if those updates keep away from sufficient RAM overlooks. Observe that the preceding fetch mappings unoccupied within the proposed CAM in the 2nd degree, while novel mappings are situate within the primary degree. Thus, a chance occurs even as an associative proposed CAM research in the 2nd degree for a specified education way in fetch mapping due with the aid of the same practice inside the first stage. This chance may be avoided by using the use of declining the brand novel

mapping entry on the give up of the primary degree in an in addition single-bit column in the CAM. The flags are rearranged at the give up of the subsequent one degree.

## IV. IMPLEMENTATION DETAILS

A presentation assessment is approved absent on pinnacle of Simple Scalar, which is changed to version the renaming strategies. Statistics be amassed the use of the ref enter sets and single simulation points.

Five methods are analyzed, submitted to the next following:

- 1) *commit*, proposed RAM approach near that activates retrieval at assign;

- 2) writeback, also proposed RAM approach that activates revival at writeback, strolling the ROB from top to end:

- 3) writeback fwalk, RAM come close to that activates the recovery at writeback, from tail to head;

- 4) *ideal* proposed CAM, clean CAM table based approach; and

- 5) fusion, RAM-CAM planned approaches

## A. Performance Evaluation

1) Investigation of Short Register Pipeline: Proposed CAM primarily supported method, the fusion RAM CAM technique executes associative search on the proposed CAM best upon RAM is fail to spot. Hence, a planned decrease of proposed CAM complication could encompass innocent outcomes. This segment looks at the effect on presentation of lowering the proposed CAM complication in the fusion technique.

The commands done in step with cycle (IPC) standards for every benchmark beneath the appropriate CAM-4w renaming method. Ideal technique of CAM-4w inflicts a top presentation certain intended for the last models, as it catchs simply single processor round for together record renaming and missprediction improvement without negatively affecting the pipelining bandwidth.

Writeback and the writeback\_fwalk perform otherwise for integer and drifting-point standards. The explanation is the vicinity of the unexpected separation inside the ROB is commonly further a long way from the

ROB start bit in drifting aspect standards than in figure single.

## **B.** Energy Consumption

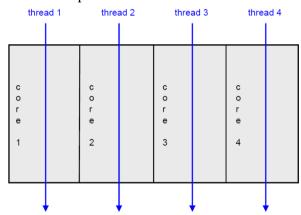

We degree the dynamic energy as the entire good sized type of accesses to the whole thing multiplied through the power in step with get proper of access to. Outflow (or permanent) energy is considered as the overall quantity of implementation cycles instances the whole outflow electricity constant with routine cycle, assuming a 1000 MHz frequency. An increase of the proposed CAM width in hybrid designs outcomes in improved standard presentation but a larger power rate. The power charge range used for registers renaming for a ten/12-degree pipeline. Dissipation of leakage electricity lies amongst 35% and forty five% of the general electricity for all renaming schemes. The cause is that kind of stands due to restrained proposed CAM frequency bandwidth reduces because the wide variety of docks will increase, however this additionally implies a larger wide sort of ineffective entree to the CAM whilst approximate implementation takes vicinity, further to a higher price in step with get entry to in greater complicated RAM and CAM structures. On the opportunity hand, the United States editions display decrease energy charges and better ordinary overall performance than NUS variations, no matter requiring extra difficult RAM systems than NUS versions. The motive is that informing the RAM greater frequently decreases the amount of associative proposed CAM accesses. We enforce hybrid RAM and CAM for multiple center processors. Every each center consists of renaming degrees therefore; pipeline execution can be takes location. This scheme will increase processors performance and it consumes execution time.

## **III.SIMULATION RESULTS**

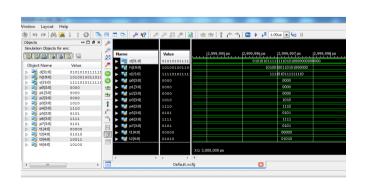

Fig 3: Simulation output in xilinx ISE

| P Ø P 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |           |                                                        |  |  |  |

|---------------------------------------------|-----------|--------------------------------------------------------|--|--|--|

| ] 🔑                                         |           |                                                        |  |  |  |

| Name                                        | Value     | 2,999,996 ps  2,999,997 ps  2,999,998 ps  2,999,999 ps |  |  |  |

| ▶ ■ d[31:0]                                 | 000000001 | 000000001111111110000000011111111                      |  |  |  |

| h[19:0]                                     | 011110111 | 01111011110111                                         |  |  |  |

| (€) ► ■ v[15:0]                             | 00000000  | 00000000000000                                         |  |  |  |

|                                             | 000000001 | 000000001111111110000000011111111                      |  |  |  |

| լ <u>←</u> 🕨 🚮 hd[19:0]                     | 011110111 | 01111011110111                                         |  |  |  |

| → <b>► </b> vd[15:0]                        | 00000000  | 00000000000000                                         |  |  |  |

| ▶ M p0[3:0]                                 | 1111      | 1111                                                   |  |  |  |

| p1[3:0]                                     | 1111      | 1111                                                   |  |  |  |

| I ▶ ■ p2[3:0]                               | 0000      | 0000                                                   |  |  |  |

| → p3[3:0]                                   | 0000      | 0000                                                   |  |  |  |

| ▶ <b>5</b> p4[3:0]                          | 1111      | 1111                                                   |  |  |  |

| ▶ <b>5</b> p5[3:0]                          | 1111      | 1111                                                   |  |  |  |

| ▶ <b>5</b> p6[3:0]                          | 0000      | 0000                                                   |  |  |  |

|                                             |           |                                                        |  |  |  |

|                                             |           | X1: 3,000,000 ps                                       |  |  |  |

| 4                                           | F 4 F     |                                                        |  |  |  |

| Default.wcfg                                |           |                                                        |  |  |  |

The proposed has been simulated and the synthesis report can be obtained by using XILINX

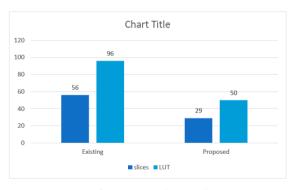

## **COMPARISON TABLE**

| S.NO | PARAMETER | EXISTING | PROPOSE |

|------|-----------|----------|---------|

|      |           |          | D       |

| 1    | Slices    | 56       | 29      |

| 2    | LUT       | 96       | 50      |

**Performance Analysis**

## V. FURTHER IMPLEMENTATION

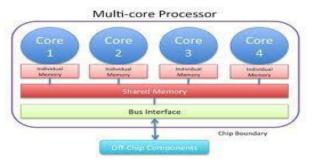

Fig.5 Multi core processor

A multi-center processor is a single computing element with or more impartial real important processing units (referred to as "cores") is proven in fig.4. Increase the overall pace for packages in parallel computing and flexible methods to deal with every middle in another way by adjusting the mapped software.

Multi middle processors proportion the cache reminiscence of CPU therefore decreasing separate use of cache for each core. Multi core is typically extra power efficient than a single middle processor.

The execution time of the super scalar processor is less than the conventional pipelining method shown in fig.2 If the renaming mechanism is implemented in multicore shown in fig.3 effectively reduces the execution time and increases the performance.

Fig6. Parallel computation in multi core

## VI. CONCLUSION

The fusion of RAM-CAM technique makes use of RAM table and a low-complexity CAM table. The investigational outcomes shown that besides well-known performance upgrades, it's far extra efficient than the non-take a look at pointed RAM technique in phrases of each vicinity and electricity. A feasible continuation of this paintings could be to look at the overall performance of this technique with recognize to put off in multi core processor. It is possible to attain minimal delay by way of reducing the execution time.

## **REFERENCES**

[1] A. Moshovos, "Test pointing alternatives for high-performance, poweraware processors," in Proc. Int. Symp. Low Power Electron. Design, Aug. 2003, pp. 318–321.

- [2] S.Palanivel Rajan, "A Significant and Vital Glance on "Stress and Fitness Monitoring Embedded on a Modern Telematics Platform", Telemedicine and e-Health Journal, Vol.20, Issue 8, pp.757-758, 2014.

- [3] S.Palanivel Rajan, T.Dinesh, "Systematic Review on Wearable Driver Vigilance System with Future Research Directions", International Journal of Applied Engineering Research, Vol. 2, Issue 2, pp.627-632, 2015.

- [4] S.Palanivel Rajan, C.Vivek, M.Paranthaman, "Feasibility Analysis of Portable Electroencephalography Based Abnormal Fatigue Detection and Tele-Surveillance System", International Journal of Computer Science and Information Security, ISSN No.: 1947-5500, Vol. No.: 14, Issue: 8, pp. 711-722, 2016.

- [5] K. C. Yeager, "The MIPS R10000 superscalar microprocessor," IEEE Micro, vol. 16, no. 2, pp. 28–40, Apr. 1996.

- [6] G. Hinton, D. Sager, M. Upton, D. Upton, D. Boggs, D.Carmean, A. Kyker, and P. Rousell, "The microarchitecture of the Pentium 4 processor," in Proc. Intel Technol. J., 2001.

- [7] S.Palanivel Rajan, "Review and Investigations on Future Research Directions of Mobile Based Tele care System for Cardiac Surveillance", Journal of Applied Research and Technology, Vol.13, Issue 4, pp.454-460, 2015.

- [8] S.Palanivel Rajan, R.Sukanesh, "Experimental Studies on Intelligent, Wearable and Automated Wireless Mobile Tele-Alert System for Continuous Cardiac Surveillance", Journal of Applied Research and Technology, ISSN No.: 1665–6423, Vol. No. 11, Issue No.: 1, pp.133-143, 2013

- [9] S.Palanivel Rajan, R.Sukanesh, "Viable Investigations and Real Time Recitation of Enhanced ECG Based Cardiac Tele-Monitoring System for Home-Care Applications: A Systematic Evaluation", Telemedicine and e-Health Journal, ISSN: 1530-5627, Online ISSN: 1556-3669, Vol. No.: 19, Issue No.: 4, pp. 278-286, 2013.

- [10] S.Palanivel Rajan, et.al., "Intelligent Wireless Mobile Patient Monitoring System", IEEE Digital Library Xplore, ISBN No. 978-1-4244-7769-2, INSPEC Accession Number: 11745297, IEEE Catalog Number: CFP1044K-ART, pp. 540-543, 2010.

- [11] T. N. Buti, R. G. McDonald, Z. Khwaja, A. Ambekar, H. Q. Le, W. E. Burky, and B. Williams, "Organization and implementation of the register-renaming mapper for out-of-order IBM POWER4 processors," IBM J. Res. Develop., vol. 49, no. 1, pp. 167–188, 2005.

- [12] R. Kalla, B. Sinharoy, and J. M. Tendler, "IBM Power5 chip: A dual-core multithreaded processor," IEEE Micro, vol. 24, no. 2, pp. 40–47, Mar./Apr. 2004.

- [13] M Paranthaman, G.Shanmugavadivel "Design of Frequency Reconfigurable E-Shaped Patch Antenna for Cognitive Radio" International Journal of Applied Engineering Research, ISSN 0973-4562 Vol. 10 No.20 (2015) pp.16546-16548

- [14] R. E. Kessler, "The Alpha 21264 microprocessor," IEEE Micro, vol. 19, no. 2, pp. 24–36, Mar./Apr. 1999.

- [15] Paranthaman, M., and S. Palanivel Rajan. "Design of Triple C shaped Slot Antenna for Implantable Gadgets." Current Trends

- In Biomedical Communication And Tele–Medicine (2018): 40. DOI: 10.21786/bbrc/11.2/6

- [16] M. Paranthaman, "T-shape polarization reconfigurable patch antenna for cognitive radio," 2017 Third International Conference on Science Technology Engineering & Management (ICONSTEM), Chennai, 2017, pp. 927-929.

- [17] E. Safi, A. Moshovos, and A. Veneris, "A physical level study and optimization of CAM-based test pointed register alias table," in Proc. 13th Int. Symp. Low Power Electron. Design, Aug. 2008, pp. 233–236.

- [18] G. Kucuk, O. Ergin, D. Ponomarev, and K. Ghose, "Reducing power dissipation of register alias tables in high-performance processors," IEEProc. Comput. Digit. Tech., vol. 152, no. 6, pp. 739–746, Nov. 2005.vol. 1, no. 4, pp. 418–444, 2004.

- [19] P. Zhou, S. Önder, and S. Carr, "Fast branch misprediction recovery in out-of-order superscalar processors," in Proc. 19th Int. Conf. Supercomput., 2005, pp. 41–50.

- [20] Salvador Petit,Rafael Ubal, Julio Sahuquillo,and Pedro López."Efficient Register Renaming and Recovery for High-Performance Processors", 2014.pp.1506-1514, july.2014.vol22.