# An Efficient Current Starved Ring VCO Using SVL Approach

V. Saraswathi<sup>1</sup>, Dr A. Sathish<sup>2</sup>, G. Madhavi<sup>3</sup>

<sup>1</sup>Assistant Professor, <sup>2</sup>Professor, <sup>1,2</sup>Department of Electronic and Communication Engineering, RGM CET, Nandyal, Andhra Pradesh saru16phd@gmail.com <sup>3</sup>Assistant Professor, Department of Electronic and Communication Engineering, Malla Reddy Institute of Technology, Telangana, India

Article Info Volume 81 Page Number: 5252 - 5255 Publication Issue: November-December 2019

# Abstract

Most of the communication standards working together today are mobile, Wi-Fi and Bluetooth on the same chip system. Voltage-Controlled Oscillator (VCO) is the key component a challenging building block in a transceiver system. It produces the local oscillator signals which are used to carry radio frequency signals in transceivers. This paper focuses on and analysis and design of current starved voltage-controlled ring oscillator. To optimize and design the voltage-controlled oscillators, carry out analysis and enhance the performance. To compare the performance of designed voltagecontrolled oscillators using different techniques against performance of voltage controlled oscillators in the base paper.

Article History Article Received: 5 March 2019 Revised: 18 May 2019 Accepted: 24 September 2019 Publication: 25 December 2019

**Keywords:** Ring Oscillator, Current Starved VCO, Power consumption, Leakage Current

# I. INTRODUCTION

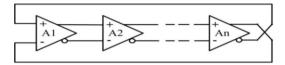

In the VLSI sector, the development of a linear, broad-band voltage oscillator to implement RF is a difficult task for Electrical Engineers. VCO is the main component in several RF systems. VCO is the heart of the Phase Lock Loop system. An oscillator is a standalone unit that generates a periodic output without an input. The VCO is an electronic circuit which produces the frequency stream according to the input voltage. VCO is the voltage of the frequency converter. The VCO's requirements are all important: frequency accuracy, wide tuner range, tuning linearity, high power consumption, small quantity and small noise [1]. VCO practices the logic of current request sensitivity mode. The current mode logic is differential logic and is mainly used in clock and data recovery applications. It is beneficial in the integrated analog and mixed signal circuit. CML provides noise immunity and produces miniature noise concentrations. The circuits have reduced distortion and enhanced ESD immunity. The differential pair VCO is a circle type oscillator as shown in the figure.1. The differential VCO couple provides the high frequency increase. First, the delay cell is created when this VCO is designed. The postpone cell has a main functional differential amplifier. The transistors of two PMOS cells removed had been designed to operate in linear proximity in order to act as variable resistors. The frequency of production is tracked with different resistors. This is owing to the reality that the frequency is based on the moment interval of the cell which is countless when using variable resistances. Rest transistors (PMOS) were performed in the saturation region. PMOS functions as conductor circuits, so we use the NMOS as a powerful charge. The type of mobile postponement with a mail limit that cannot maintain the load voltage swing regularly. It occurs because the voltage of the switch differs from favorable input voltage to adverse output voltage. It occurs because the strength in the entire transistor (PMOS) generally varies if the control voltage shifts. The trade in these numbers leads the production swing to change and causes non-linearity. The approach for this benefit is to make the system bias rather than the single channel biasing of each stage. It makes the design simpler. Current is governed by the voltage Vb1 and Vb2 of the power panel at each point of the differential oscillator. It therefore regulates the duration of each loop, thus improving or reducing the oscillation

frequency for each phase. Greater degree distribution lead to a decrease in the frequency range because the ratio between the frequency range and the two cases of error in each spectrum and the degree of a lower amount exists. As a consequence of the velocity energy trade, this is suitable for reduced broad areas of structures for size, therefore seven level differential combinations are used in this layout. The scheme shows that the control voltage is placed into the differential step previously, which distinguishes each differential phase of the differential VCO. The interval of each phase determines the frequency of the production clock. The interval is controlled by the voltage. The enormous tuning range of each phase provides a broad range of frequencies.

Figure 1. Differential Ring oscillator

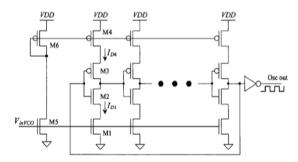

The current starved VCO schematic is shown in Figure 2. Its procedure is like the oscillator of the ring. As an inverter, MOSFETs M2 and M3 function and MOSFETs M1 and M4 are currently used as inputs. The current sources, M1 and M4, restrict the accessible present for the M2 and M3 transistors. Putting in other way, the inverter is starved. The MOSFETs M5 and M6 drain current flows are identical and are arranged by input control voltage. In each inverter / current origin phase the current flows in M5 and M6 are reflected.

Figure 2. Schematic of Current Starved VCO [2]

In recent times, SVL is the most common methodology in the sector. It is used to decrease power consumption and current leakage. The suggested study verifies SVL's evaluation of VCO starved current and demonstrates that the SVL method used for voltage storage results in an unnecessary drop in the leakage current. In this paper, the starved VCO is done using the SVL method.

The main contributions and organization of this paper are summarized as follows: In section II we describe literature review of different schemes for VCO schemes. The section III proposed work. Finally in section IV we concluded the paper.

### **II.** RELATED WORKS

In [3], the authors suggested that currently starved CMOS VCO with an extremely low power and low noise. Power and loop region are much less helpful for mobile appliances. Phase noise and transient response were performed at 1MHz, and phase noise was -104,0dBc / Hz with 1V supply voltage. In [4] the authors suggested in this document that CSVCO and DAVCO frequency analyzes were carried out using 350nm of CMOS technology. Different parameters, like tuning spectrum, frequency response and CSVCO and DAVCO energy dissipation have been contrasted in the same background. In [5] the writers proposed that the PLL was built with VCO cap at 3V voltage with 180nm CMOS technology. The proposed VCO ring was used to implement PLL in the frequency range of GHz. The PLL power dissipation is only 28mgw with a 2.5GHz frequency. In [6], the authors suggested that 3-stage Ring Oscillator with 90nm CMOS technology was designed. For simulation, supply voltage of 1.8V was used. The voltage of the control was varied from 0V to 0.6V. The linear tuning attributes of 4.52GHz to 6.02GHz have been achieved. The circuit's power dissipation is 0.295 milliwatts.

#### III. PROPOSED FRAMEWORK

Amongst the most significant fundamental construction buildings in analog and digital circuits is a voltage-controlled oscillator (VCO). In a wireless scheme the performance of the communications link is primarily determined by the features of the VCO and the VCOs require higher frequency ranges in today's wireless communication schemes. VCOs used in low frequency devices traditionally have been used with CMOS technology, but submicron procedures have permitted CMOS oscillators to attain gigahertz frequencies. The use of instant swing command makes this variety feasible. Sometimes using circuit methods, VCO can be constructed. The fluctuating input signal is readily designed by the same pulsation of the output signal. The design is implemented in a 45 nm CMOS technology cadence virtuoso instrument with 0.7V energy. Measured performance demonstrates that the present trapped voltage-controlled oscillator decreases leakage current, noise, and power usage in SVL technology. SVL method is the most prevalent methodology in the sector in latest moments. SVL method is used to decrease energy usage and current leakage. The suggested study verifies the SVL assessment of starved VCO and demonstrates that the SVL technology implemented for the storage voltage reduces unnecessary leakage resistance. Current VCO works using SVL method in this section.

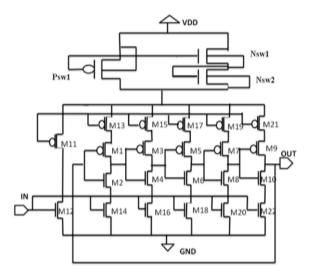

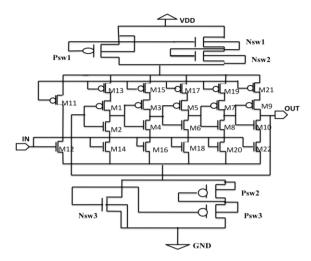

Figure 3. Schematic view of U-SVL Technique

It is better than CMOS technologies. On the current Starved VCO loop, self-voltage method is implemented. The SVL loop usually includes a lower SVL and an upper SVL. The SVL system (lower and upper) is used one by one on the loop and multiple system parameters such as leakage, leakage capacity, noise and power usage are calculated as shown further in the outcomes of the investigate. The system operates in two forms, the current mode and the standby mode. Active method is the regular load circuit operating method, whereby the higher and smaller SVL circuits which are better suited to create the current load circuit of the VCO starved operate usually to generate its required features. The charge loop prevents its usual procedure in standby condition.

# Upper SVL Technique

When the load circuit is active, in this instance, the upper SVL switches on p-MOSFET (Psw1) and turns off both n-MOSFET (Nsw1 and Nsw2) resistors in the active mode of Figure 3. So turn ON p-MOSFET.

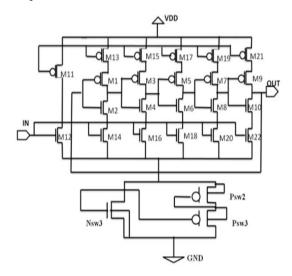

Figure 4. Schematic view L-SVL Technique

Figure 5. Schematic view of combined (LSVL + USVL) technique

# Lower SVL Technique

In the active mode as shown in Figure 4, the circuit turns on the n-MOSFET (Nsw3) and offs both the Psw2 and the Psw3 resistors serially linked. Thus ground supply is directly connected to the circuit for application by ON n-MOSFET. On the other hand, the standby mode as a reference, the nMOSFET button is OFF and the p-MOSFET resistance, the turn ON, is connected to the circuit by a ground supply.

Current Starved Voltage Controlled Oscillator Using Combined (LSVL + USVL)

The upper and lower SVL are applied together to the load circuit as shown in Figure 5.

The decreased supply voltage and enhance ground voltage level to the circuit in standby mode of operation and support normal supply voltage and ground voltage in the active mode.

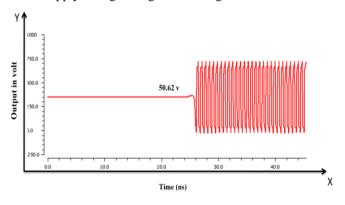

Figure 6. Ring Oscillator Transient Response

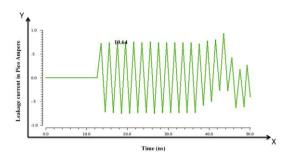

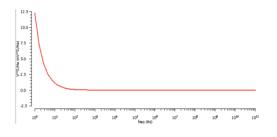

Figure 7. Leakage Current versus Time Graph

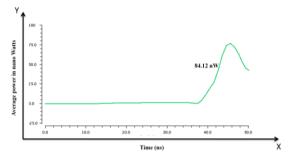

Figure 8. Average Power versus Time Graph

Figure 9. Noise Waveform of Current Starved VCO Using Combined (U-SVL and L-SVL) Method

# **IV.** CONCLUSION

In this paper, a new method of leakage reduction for SVL oriented present starved VCO is used to improve efficiency in terms of leakage, power and noise. The effectiveness of the suggested methods for reducing leakage is proved via USVL, LSVL and then combined in the loop. Compare the efficiency of engineered voltage controlled oscillators with the results of VCO's by using various methods.

# REFERENCES

- [1] Floyd M Gardner, Phase Lock Techniques, 3rd ed., Wiley Interscience Publication, 2005.

- [2] R. Jacob Baker. CMOS circuit design, Layout and simulation, John Wiley and Sons Inc, Publication, 2010.

- [3] Suraj Kumar Saw, Vijay Nath, "An Ultra-Low Power And Low Phase Noise Current Starved Cmos Vco For Wireless Application", 2015 Interation Conference on Industrial Instrumentation and Control (ICIC) College of Engineering Pune, India May 28-30, 2015.

- [4] Balodi, Deepak, Arunima Verma, and PA Govidacharyulu SMIEEE. "Study and Design of Standard PLL with Comparative Analysis between Current Starved VCO and Differential Pair VCO."

- [5] Shruti Suman, K. G. Sharma, P. K. Ghosh, "Design Of PLL Using Improved Performance Ring VCO", International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT) – 2016.

- [6] Rafiul Islam, Ahmad Nafis Khan Suprotik, Md. Tawfiq Amin, "Design and analysis of 3 stage ring oscillator Based on MOS capacitance for wireless applications "2017 International Conference on Electrical, Computer and Communication Engineering (ECCE).