# Reproducible MAC units using Fir Filter Design

Mr. Sonu kumar<sup>1</sup>, Dr.Pradeep kumar<sup>2</sup>, Dr.Prasad Janga<sup>3</sup> <sup>1</sup>PG Scholar, Department of ECE, CMR Institute of Technology, Hyderabad <sup>2</sup>Associate Professor, Department of ECE, CMR Institute of Technology, Hyderabad <sup>3</sup>Professor, Department of ECE, CMR Institute of Technology, Hyderabad <sup>1</sup>sonukumarjha9177@gmail.com,<sup>2</sup> pra\_deep\_jec@yahoo.co.in,<sup>3</sup>prasadjanga85@gmail.com

Article Info Volume 83 Page Number: 7535 - 7538 **Publication Issue:** March - April 2020

Article Received: 24 July 2019

Revised: 12 September 2019

Publication: 07 April 2020

Article History

### Abstract

In digital signal processing, filters are being used in almost all devices. The useful part of the signal is being used by the filter, and the required parts of the signals are delivered to the receivers. The FIR"s filters is an combination of multiplier and additive, which is use for devices with linear characteristic. In this paper the FIR filter is structured using a reusable Radix's 4 booths multipliers and a Ripple carry additive. A mixture of Radix 4, Booths Multipliers & Ripple Carry Add makes the FIR's filters fasters. The RTL's mixture is terminated using Xilinx 14.7 and reproduction is terminated using Xilinx. In this work we contrast the Finite Drive Reaction filter and the MAC unit and comprising of Radix 4 booth multiplier with FIR filter with Vedic multiplier. By the proposed work of FIR filter with MAC unit we can get effective results In' term off size, detection & powers consumptions aspects.

Accepted: 15 February 2020 Keywords; Recoverable booth multipliers, Wave carrying connector, MAC's units, Configurations registers, Recoverable FIR"s Filters.

# I. IMPLEMENTATION OF PROPOSEDS

MAC'S UNIT

The proposed MAC's units is a coalition off recurring booths multipliers [2] & looks for further additions. The recoverable booth multipliers are proposed in the subpart and the full MAC's units as indicated in the subtype.

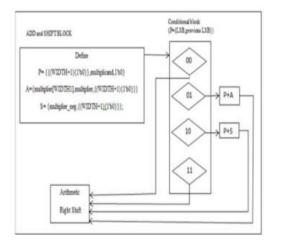

Reusable Booths Multipliers: **Booths** multipliers are better multipliers because it's reflects the standards structures & rapidly degrades fractional objects. [5]. A reconstructable booth multiplier has been proposed [2] that can work for the number of bits. A finite state machine has been used in its center programming which simplifies calculations. This can be accomplished for both very well-marked and unrelated numbers. [6]. The recoverable booths multipliers we use for our proposed works dependency on existing booths. The construction of the proposed booths multipliers as shown in the fig. A configuration register for this

proposed work incorporates the central module of the recoverable booth multiplier. The accepted count is set to n = 16 bits, on any model we need an extension for any 4 bit number. In any case, It is considered a 16 bits numbers, it's consume more clocks cycles. So a configuration register is displayed that is set to 4 bits,8 bits & 16 bits to keep the good methods important from this issue. The configurations file is set as 001. as long as we need a 4 bit result. For 8 bits It's set to 010 & for a 16 bits configurations file it's set to 100. The configurations file is longer for 4 bits. LSB's which is 001. Just like they have a 32 bits thing, only 8 bit are important anyway, so it will take to adjusting parts out of the thing. For a 4 bit count the portion removed from 16 bits is from twentieth to thirteenth. If estimation is practiced for 8 bits, by then the configuration register for the second piece from the LSB is high. Again the thing is 32 bits for 8 bit estimation. We have to extract the part from the 24th to the ninth part. This is the useful part and we get the 16 bit 7535

yield of the final results of FIR's filters. Fig.2. displays a stream plot in which we have shown the reusable booths multipliers [4] with the probability of configurations file. The configuration register for the 16 bits information will be higher for the MSB's bits which is 100's & nothing will be removed.

Fig.1. Reconfigurable Booth multiplier

# Fig.2. Reusable booth multiplier with the concept of configuration registers on the flow chart

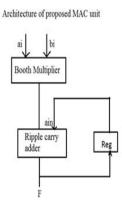

B. The proposed MAC's units is show in fig. 3. As show in the Mac unit, the first of the two commitments. The multiplier booth is copied using the reconfigurable and then the development result is added. Previous set results of MACs units. This can be appreciated as we go with the model: one is the data AI derivative that is tolerating all through all computations. Another data is the bi which is the FIR's filters coefficients. Theses 2 data sources are expanded using the recoverable booth then multiplier and the results are then fed to the Ripple Carter adder. Another variable is Ann. In the next cycle, Ann is currently the previous yield of the MAC unit. as per a file is used in the programme required to use the file. They have ability and next commit for the additive in the future chain.

# Fig.3. Architecture of the proposed MAC unit

## **II. RESULT AND COMPETITIVE ANALYSIS**

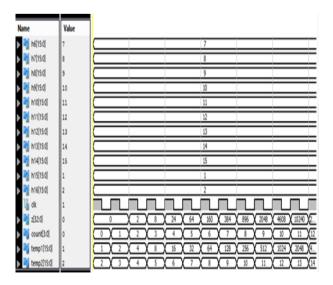

The proposed FIR's filter's is' an instant filter's. Santosh's et.al. [1] has demonstrated FSM-based filters using's the transformed booths multiplier's and ripple handle add square, while ours proposed works show as faster FIR's filters using the recycled booth's multiplier's & the ripple handle add to the final state machine. Reusable Booth Multiplier is proposed [2]. The language used to make the arrangement is Verilog HDL. Reunion and association have been performed on various devices. Modelim 6.4a has been used for Mix Exilinks 14.3 for multiplication. Proposed works in summer &

evaluation with' Santosh's Singh al...[[1] Independently shown' in the Table's1 & Table's2. The safe decision for' the proposed MAC' unit's 9.42 Nm & 0.158 watts of power out. This' works relies on a quickly reconstructable booth multiplier that relies on, FSM's .The FIR's filters is proposed for, the numbers of bits, & for' this proposed works sets contrast to, bits & calculated to 4 bits. The result of the recoverable multiplier is 32 bits with twentieth to thirteenth bits removed for yield.

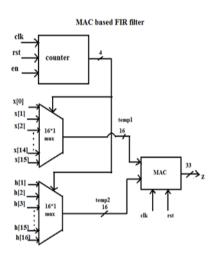

### Fig.4. block diagram of fir filter based mac unit

### **III. SIMULATION OUTPUT**

Simulation Report For Radix 4 Multiplier Based Fir Filter

**Table 1: Comparisons table**

|                                               | Area                  | Delay<br>(ns) | Power<br>(mw) | Freque<br>ncy<br>(Mhz) | throughput |

|-----------------------------------------------|-----------------------|---------------|---------------|------------------------|------------|

| Vedic<br>multiplie<br>r based<br>fir filter   | 579<br>out of<br>8672 | 35.179        | 0.159         | 28.426                 | 0.103      |

| Radix-4<br>multiplie<br>r based<br>FIR filter | 60 out<br>of<br>8672  | 9.42          | 0.158         | 106.08<br>1            | 1.441      |

| IV. CONCLUSION                                |                       |               |               |                        |            |

An FIR filter is planned using the reconfigurable Booth multiplier. The rebuildable multiplier is dealing with the state machine. The proposed FIR filter is organized using behavioral illustration. The proposed actions have been adequately aligned. The proposed MAC,s units cans works for' bit numbers. The association for 16 bits is practiced for this paper. The MAC's unit is the fast units that make FIR's filter fasters. We found progressively appropriate results in the proposed scheme of Radix's four booths multipliers for successive areas, delay & repeat factors.

### **REFERENCE'S**

- [1] Santosh'sh BbM., Chirag's., "FPGA Applied Quantification of Qualified FIR Filters with Determined Point Coefficients" IEEE's International Conference on Emeg.., Trends Communications, pp. 1-6,2013.

- [2] Deepika Nidhis, "RTL Design of Reconfigurable Multipliers", IEEE., International Conference in Soft Computing Techniques & Implementation, pp.24/28/2015.

- [3] M.Sai Kumar, D.Ashok Kumar, P.S., "Design and Performance Analysis Multiplayer MAC Unit", IEEE International Confer., in Circuits, Power & Computing Technologies, PP.1084/1089/ 2014.

- [4] D.J.Kumar,E.L., "Performance Analysis of FIR Filters Using Booth Multipliers", IEEE International Conference in Current Trends in Engineering & Technologies, PP.414-417-2014.

- [5] Manoj Sharma, Richa Verma, "Reduction

Published by: The Mattingley Publishing Co., Inc.

7537

(reduction)" (Negative) Partial Product for Radix4Booth'sAlgorithm", IEEE World Congress on Information & Communication Technology, Pp.1169=1174= 2011.

- [6] Rabindra P.Rajput,N. Shankamukhaswamy, "High Speed Modified Encoder Multiplier for Signature and Unsigned Numbers", IEEE International Conference on Modeling&Simulation,pp.649-654,,2012

- [7] D. Jacquelmoni, P.Eben Sophia, "Design of lowpower and high-speed configuration booth multipliers", IEEE International Conference on Electronics Computer Technology, Vol.-6, PP..338-342/2011

- [8] 8.S. Rajput, R.Shukla, P.Praveen, A.Anand, "Implementation of Novel Radix-4 Booth Multiplier Based High Speed and Low Power Hybrid Additives", International Conference on IEEE Communications Systems and Network Technologies, pp.-741-743., 2013

- [9] Z.Shhun, O.A.Pfander, H.J.Pfleiderer & A.Bermak, "A VLSI Architecture Run-Time Multi-Precision Reconfigurable Booth Multiplier", IEEE International Conference on Electronics, Circuits & System,, pP.975/978/for2007.