# A Review of Formal Verification Methodologies for HDL Designs

Mrs.V.Uma, Assistant Professor/ECE, SCSVMV Umabala.ece@kanchiuniv.ac.in Dr.Ramalatha Marimuthu Professor/ECE Kumaraguru Institute of Technology ramalatha.marimuthu@gmail.com

Article Info Volume 82 Page Number: 5464 - 5468 Publication Issue: January-February 2020

Article History Article Received: 18 May 2019 Revised: 14 July 2019 Accepted: 22 December 2019 Publication: 27 January 2020

#### Abstract:

HDLs can be used to design and describe the digital system layouts from flip-flop memory to complex communications interface protocols. The HDL designs can be described the operations and structures in gate level and Register Transfer level. This paper reviews the HDL design verification concepts and its conditions, general verification methods and also compares the basic verification procedure. Itbriefly describes and discusses their advantages and disadvantages. In this paper, we will discuss in detail about different verification methods for HDL designs.

Keywords: HDL design, Formal Verification, Logic Simulaion.

## I. Introduction

In formal verification of HDL designs, the design and specification are translated into arithmetical models. Formal verification methodologies are used to validate a design by proving the design accuracy correctly. Hence, the techniques of formal verification can verify the whole HDL designcomprehensively <sup>[1]</sup>. For the verification of software and hardware designs, a Formal verification technique has been used.

The formal verification must be completed such that some other third parties are proficient to validate the accuracy with smalltry. The aim of this technique to give a proof of design accuracy that can be checked automatically. Particularly, all significant designs should be followed in form of a four kinds, they are i) the design, ii) a requirement, iii) a human-readable verification, and 4) a machine demonstrated evidence. In this paper, the formal verification methodologies of HDL designs have been reviewed.

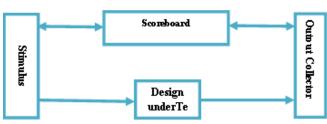

Figure 1 Verification Environment

#### II. Formal Verification Methodologies

The safety properties of formal verified design to optimized cache coherence protocols explained in. This paper develops the design appropriateness issue for highly developed cache logic protocols which will be hierarchically planned for the scalable designs. To resolve the issue, the authors developed a compositional methodsfamilydepend on assume-guarantee analysis in for sinking the complexity of verification.

And they also developed fault trace validation techniques to remove fake alarms using heuristics that take advantage of presume guarantee methods. This method needs no particular tool support. The Murphi model checker tool is used for concept and fault trace validation.

Described the back-to-back formal Instruction Set Architecture verification of RISC-V processors. The majorobjective of this article is to check a hardware model for safety properties. The biggest field of the formal verification is the Hardware model checking because it can be automatically verifying the accuracy properties of finite state systems.

The advantage of end to end verification is to create the information of the chosen actions portable between implementations and it is simple to compare the formal description. The disadvantage of the method is to prove big end to end properties and it is computationally exclusive. The instruction and consistency checks are the two methods utilized to validate a RISC-V processor. It sustains for more ISA extensions like RV64 in future. And also support for CSR's.

Thomas Brabant investigated the formal verification of an optimized compiler, applying the thoughts following the compeer (compiler that produces ARM and RISC-V assembly code from language)method to the synthesis C of hardware<sup>[3]</sup>. Using Parametric Higher-Order Abstract Syntax (PHOAS) to insert a section specific language makes it possible to employ Coq (Certified Meta programming tool) to explain the digital circuits. Machine checked proofs of accuracy are used for several simple designs of hardware. It gives a proficient path to certification of parameterized designs of hardware.

A high level parametric requirement of hardware and its modular confirmation has been investigated in. By using Blue spec language, are cords of Coq that utilizes labeled conversion systems to permitrelatedcommunicative and modular reasoning for the design of hardware has been presented in kami<sup>[4]</sup>. Developed and verified the RTL designs fully within Coq, finishing withregularextractioninto a pipeline that bottoms out in FPGAs.

This paper explains a designed and demonstrated multicore system containing RISC-V cores. RISC-V components are verified and planned to level up the realism stage by designing additional complex processor optimization Kami would be maintaining verification of likeness properties (something good eventually happens) similar to deadlock freedom verification that can be applied to the software architecture.

presented the verification of control logic methods of pipelined microprocessor. For verification, the central processing unit time needed and it is independent of the register file size, the data path width and the number of Arithmetic Logic Unit operations. The data information debugging is generally developed for incorrect designs of processor. It is very challenging to enhance the verification tool capacity as fast as designers are improving the scale of the issue. Explained the verification of SOC designs. This paper presents the hardware extension that permits to synthesize checker in the process of verification. An on-line verification methodology is allowed the design of System OnChip. A software level can be directly connected to the formal verification. Described the Burch and Dill flushing method of superscalar microprocessor. The ALU, instruction and data memory have an arbitrary delay. The success of this technique is proficient formal verification of a particular problem of pipelined DLX with multi cycle purposeful units and branch calculation.

On bridging model and formal verification has been explained in Formal verification are two corresponding methods for examine the accuracy of software and hardware designs. Formal verification proves that a design property holds for all points. The simulation works unexpectedly well attractive into report the insignificant division of the investigate gap enclosed by analysis points. Investigate this fact by the instance of the satisfiability issue (SAT). The ample test position of a formula CNF as a check set encrypting a formal confirmation that this formula is unsatisfiable. It illustrates how ample test sets can be built. An application of rigid ample test sets for testing technical errors and design changes and provides a few tentative results.

The formal verification research has been discussed in.The hardware and software formal verification research has been achieved significant progress in the techniques development and tools to gather the enhancing system complexity. The formal verification role is to discover the faults and to enhance the dependability on the system design correctness.

The main aim of this study is to present a methodicalanalysis of the survey to create the position of the art investigate in formal verification. Performing the systematic analysis to literature can be separated into three important stages; they are preparation, implementation and documentation. During the last decades, to find the methods, approaches and research methodologies used and the force of these study activities. Evidence based research was used to achieve.

System On a Chip designs are an incorporation of several modules and cores. SoC incorporation is an outcome of integrating a small number of chips together. In the overall design effort, Standalone logic verification design is one of the most significant steps. Two logic verification methods are normally used when verifying a SOC: formal based verificationand simulation based verification.

# III. Formal Verification of Hardware Design

In the design of hardware formal verification has been discussed by Christopher. The methods of formal verification have an optional method to ensuring the correctness and quality of designs. The testing and simulation are the techniques of validation.The formal methods were useful to the designs of industrial-scale like microprocessors, interfaces, memory subsystems and hardware communications.

Formal methods have emerged as a different come up to ensuring the feature and accuracy of hardware designs, overcome various limits of conventional validation techniques such

as testing and simulation. The proper framework used to identify preferred properties of a design and the verification methods and tools used to cause about the association between a requirement and an equivalent implementation. Described the formal verification to verify the hardware correctness and need appropriate systems and automated proofs. All phases of design, covering firmware, software, and hardware are in the domain of verification spans. The difference between formal and simulation based verification lies in the occurrenceof mathematical proof, it isimportant have formalism to а to characterizehardware systems at all concept in. The two main classes of properties are safety and liveness properties. "Bad things will never happen" is called safety properties. "Good things will happen in the future" is called Liveness properties proposed the efficient verification algorithmic methods for accurate parameterized analysis about cache coherence protocols. This paper introduces he model of guarded broadcast protocols. It illustrates how atheoretical history graph construction can be utilized to cause about protection properties for this framework. This verification methodology is applicable to both likeness and safety properties. At last, this methodology is used for reducing parameterized analysis about directory based protocols to snoopy consequently leveraging methods protocols, developed for verifying snoopy protocols to directory based ones. Explained the digital system of formal verification. The model and equivalence checking of sequential circuits that uses Binary Decision Diagram (BDD). The correctness of a design is mathematically proved in formal verification methods. The main issue of formal verification, the target size is increased and it takes long time to verify the designs. Sometimes, the verification method failed. <sup>[11]</sup> Developed the verification techniques that are very strong to resolve the issue.

A structured method of VLSI designs has been discussed by Dan R.chica. From the higher

order functional languages for hardware synthesis are depend on Reynold's Syntactic control of interference. By game semantics, it used the semantic model. An important characteristic in the framework of hardware compilation and reprocess a conventional game model to make simpler accuracy proofs. The design of asynchronous event-logic circuits, which obviously equivalent the asynchronous model of the HDL language.

SaiqaBibi has discussed the formal methods for commercial applications issues<sup>[18]</sup>. The profit contain issues establish in prior step of software development, automating, verifying the assured properties and minimizing redraft. Formal methods offer numerous advantages that is exploit automation with automated tools, automatic verification enhancement cost saving, fault reduction and quality enhancement. These profit are the incentive to use formal methods in commercial software industry. The goal of this study is to support formal methods for profitable application software in industry.

A purposeful Self-Test Methodology for Processors has been discussed by [16]. BIST techniques are not capable to compact with big designs without adding together high test overhead. А functional self-test that is deterministic in environment. This method has the fault coverage benefit of structural testing and the at-speed benefit of functional testing, by targeting the structural test require of convenient apparatus with the assist of processor functionality. Jerry R. Burch described a method for verifying the logic of pipelined microprocessors. It handles additional difficult designs, and needs fewer human interventions, than traditional methods. The CPU time required for verification is autonomous of the data path width.Debugging information is repeatedly created for incorrect processor designs. A large amount of the power method results from an proficient strength checker for a logic of continuous functions with equal opportunity.

# IV. Conclusion

This article surveys the formal verification methodologies for HDL designs. The main aim of this survey was to analyze the formal verification methods, which are proficient to provide a full coverage for a part of hardware and software. From the above literature analysis, we found that one of the most recent formal verification methods for verifying the digital designs.

## V. References

- Jain, J., Narayan, A., Fujita, M. and Sangiovanni-Vincentelli, A., 1997, October. A survey of techniques for formal verification of combinational circuits. In Proceedings International Conference on Computer Design VLSI in Computers and Processors (pp. 445-454). IEEE

- Chen, X., Yang, Y., Gopalakrishnan, G. and Chou, C.T., 2010. Efficient methods for formally verifying safety properties of hierarchical cache coherence protocols. Formal Methods in System Design, 36(1), pp.37-64.

- 3. Wolf, C., 2017. End-to-end formal ISA verification of RISC-V processors with riscv-formal. In 7th RISC-V Workshop Proceedings, November (p. 13).

- Braibant, T. and Chlipala, A., 2013, July. Formal verification of hardware synthesis. In International Conference on Computer Aided Verification (pp. 213-228). Springer, Berlin, Heidelberg.

- 5. Choi, J., Vijayaraghavan, M., Sherman, B. and Chlipala, A., 2017. Kami: a platform for highlevel parametric hardware specification and its modular verification. Proceedings of the ACM on Programming Languages, 1(ICFP), p.24.

- Burch, J.R. and Dill, D.L., 1994, June. Automatic verification of pipelined microprocessor control. In International Conference on Computer Aided Verification (pp. 68-80). Springer, Berlin, Heidelberg.

- Drechsler, R., 2003, May. Synthesizing checkers for on-line verification of system-onchip designs. In Proceedings of the 2003 International Symposium on Circuits and Systems, 2003. ISCAS'03. (Vol. 4, pp. IV-IV). IEEE.

- 8. Velev, M.N. and Bryant, R.E., 2000. Formal verification of superscalar microprocessors

with multicycle functional units. In Carnegie Mellon University.

- 9. Kern, C. and Greenstreet, M.R., 1999. Formal verification in hardware design: a survey. ACM Transactions on Design Automation of Electronic Systems (TODAES), 4(2), pp.123-193.

- Camurati, P. and Prinetto, P., 1988. Formal verification of hardware correctness: Introduction and survey of current research. Computer, 21(7), pp.8-19.

- Emerson, E.A. and Kahlon, V., 2003, October. Exact and efficient verification of parameterized cache coherence protocols. In Advanced Research Working Conference on Correct Hardware Design and Verification Methods (pp. 247-262). Springer, Berlin, Heidelberg

- Fujita, M.A.S.A.H.I.R.O., Komatsu, S.A.T.O.S.H.I. and Saito, H.I.R.O.S.H.I., 2005. Formal verification techniques for digital systems. Dependable Computing Systems. J. Wiley.

- Ghica, D.R., 2007, January. Geometry of synthesis: a structured approach to VLSI design. In ACM SIGPLAN Notices (Vol. 42, No. 1, pp. 363-375). ACM.

- Ghica, D.R. and Smith, A., 2010. Geometry of Synthesis II: From games to delay-insensitive circuits. Electronic Notes in Theoretical Computer Science, 265, pp.301-324.

- Gunes, M., Thornton, M.A., Kocan, F. and Szygenda, S.A., 2005, August. A survey and comparison of digital logic simulators. In 48th Midwest Symposium on Circuits and Systems, 2005. (pp. 744-749). IEEE.

- 16. Chen, L. and Dey, S., 2000, April. DEFUSE: A deterministic functional self-test methodology for processors. In Proceedings 18th IEEE VLSI Test Symposium (pp. 255-262). IEEE.

- 17. Segev, E., Goldshlager, S., Miller, H., Shua, O., Sher, O. and Greenberg, S., 2004, comparing December. Evaluating and simulation verification vs. formal verification level design. approach on block In 2004 Proceedings of the 11th IEEE International Conference on Electronics, Circuits and Systems, 2004. ICECS 2004. (pp. 515-518). IEEE.

- Bibi, S., Mazhar, S., Minhas, N.M. and Ahmed, I., 2014. Formal Methods for Commercial Applications Issues vs. Solutions. Journal of Software Engineering and Applications, 7(08), p.679.

- 19. Edgar, S.M. and David, M.V., 2014. State of the Art in the Research of Formal Verification.Ingeniería, Investigación y Tecnología, 15(4), pp.615-623.

- Goldberg, E., 2008, January. On bridging simulation and formal verification. In International Workshop on Verification, Model Checking, and Abstract Interpretation (pp. 127-141). Springer, Berlin, Heidelberg.