Article Info Volume 84

**Page Number: 06 - 18**

January - April 2021

**Publication Issue:**

Article History

Article Received: 4 October 2020

Revised: 14 November 2020

Accepted: 22 December 2020

Publication: 23 January 2021

# Harmonic Reduction in Five Levels UPFC Using SVPWM

Research scholar<sup>1</sup>, PhD<sup>2</sup>

## <sup>1</sup>R. Jayachandra, <sup>2</sup>Prof. G. Tulasi Ram Das

Abstract

This paper proposed real and reactive power controlled by using SVPWM for a five level unified power flow controller (UPFC). The basic control for the five levels UPFC is such that the series converter of the five levels UPFC controls the transmission line real/reactive power flow and the shunt converter of the five levels UPFC controls the five levels UPFC bus voltage/shunt reactive power and the DC link capacitor voltage. In steady state, the real power demand of the series converter is supplied by the shunt converter of the five levels UPFC. To reduced reactive power and total harmonic distortion (THD) by using SVPWM for a five levels UPFC. The SPWM using for five levels UPFC the reactive power demand is 10MVAR and total harmonic distortion (THD) is 9.01% occurred. For this reason SVPWM is proposes to reduced reactive power demand 9.5MVAR and total harmonic distortion (THD) 4.85%. A new SVPWM for a five level UPFC has been designed to limit excessive voltage excursions during reactive power transfers. PSCAD-EMTDC simulation results have been presented to show the improvement in the performance of the five levels UPFC control with the proposed reactive power and total harmonic distortion.

**Index Terms:** Unified power flow controller (UPFC), Shunt converter, Series converter, Synchronous d-q frame, Space vector PWM, DC link capacitor, PI controller.

## **I.INTRODUCTION**

UPFC is the most comprehensive multivariable flexible ac transmission system (FACTS) controller. Simultaneous control of multiple power system variables with UPFC possessed enormous difficulties. In addition, the complexity of the UPFC control increases due to the fact that the controlled and the control variables interact with each other. UPFC which consists of a series and a shunt converter connected by a common dc link capacitor can simultaneously perform the function of transmission line real/reactive power flow control in addition to UPFC bus voltage/shunt reactive power control [1].

The shunt converter of the UPFC controls the UPFC bus voltage/shunt reactive power and the dc link capacitor voltage. The series converter of the UPFC controls the transmission line real/reactive power flows by injecting a series voltage of adjustable magnitude and phase angle. The interaction between the series injected voltage and the transmission line current leads to real and reactive power exchange

Published by: The Mattingley Publishing Co., Inc.

between the series converter and the power system.

Under steady state conditions, the real power demand of the series converter is supplied by the shunt converter. But during transient conditions, the series converter real power demand is supplied by the dc link capacitor. If the information regarding the series converter real demand is not conveyed to the shunt converter control system, it could lead to collapse of the dc link capacitor voltage and subsequent removal of UPFC from operation.

Very little or no attention has been given to the important aspect of coordination control between the series and the shunt converter control systems [2]–[15]. The real power coordination discussed in [15] is based on the known fact that the shunt converter should provide the real power demand of the series converter. In this case, the series converter provides the shunt converter real power reference that includes the error due to change in dc link capacitor voltage and the series converter real power demand.

The control system designed for the shunt converter in [15] causes excessive delay in relaying the series converter real power demand information to the shunt converter. This could lead to improper coordination of the overall UPFC control system and subsequent collapse of dc link capacitor voltage under transient conditions. This is due to the fact that any change in transmission line reactive power flow achieved by adjusting the magnitude/phase angle of the series injected voltage of the UPFC is actually supplied by the shunt converter.

This aspect of UPFC control has also not been investigated [2]–[15]. The SPWM using for five levels UPFC the reactive power demand is 10MVAR and total harmonic distortion (THD) is 9.01% occurred. In this paper proposes real and reactive power controlled by using SVPWM for a five level unified power flow controller (UPFC). The basic control for the five levels UPFC is such that the series converter of the five levels UPFC controls the transmission line real/reactive power flow and the shunt converter of the five levels UPFC controls the five levels UPFC bus voltage/shunt reactive power and the DC link capacitor voltage.

In steady state, the real power demand of the series converter is supplied by the shunt converter of the five levels UPFC. To the reduced reactive power and total harmonic distortion (THD) using by SVPWM for a five levels UPFC. For this reason SVPWM is proposes to reduced reactive power demand 9.5MVAR and total harmonic distortion (THD) 4.85%.

A new SVPWM for a five level UPFC has been designed to limit excessive voltage excursions during reactive power transfers. PSCAD-EMTDC simulation results have been presented to show the improvement in the performance of the five levels UPFC control with the proposed reactive power and total harmonic distortion.

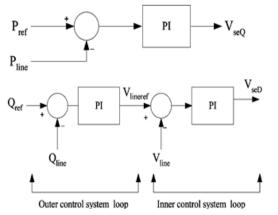

Fig.1. De-coupled D-Q axis shunts converter control system.

# **II. CONTROL STRATEGY FOR UPFC**

A. Shunt Converter Control Strategy

The shunt converter of the UPFC controls the UPFC bus voltage/shunt reactive power and the dc link capacitor voltage. In this case, the shunt converter voltage is decomposed into two components. One component is in-phase and the other inquadrature with the UPFC bus voltage. Decoupled control system has been employed to achieve simultaneous control of the UPFC bus voltage and the dc link capacitor voltage.

### B. Series Converter Control Strategy

The series converter of the UPFC provides simultaneous control of real and reactive power flow in the transmission line. To do so, the series converter injected voltage is decomposed into two components. One component of the series injected voltage is in quadrature and the other inphase with the UPFC bus voltage. The quadrature injected component controls the transmission line real power flow. This strategy is similar to that of a phase shifter.

The in-phase component controls the transmission line reactive power flow. This strategy is similar to that of a tap changer.

# **1. BASIC CONTROL SYSTEM**

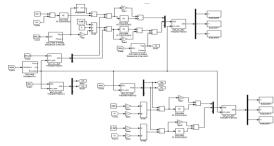

A. Shunt Converter Control System Fig. 1 shows the de-coupled control system for the shunt converter. The D-axis control system controls the dc link capacitor voltage and the Q-axis control system controls the UPFC bus voltage /shunt reactive power.

January - April 2021

The details of the de-coupled control system design can be found in [16], [17]. The de-coupled control system has been designed based on linear control system techniques and it consists of an outer loop control system that sets the reference for the inner control system loop. The inner control system loop tracks the reference.

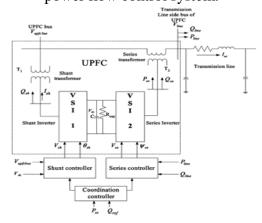

Fig.2. Series converter real and reactive power flow control system.

Fig.3. UPFC connected to a transmission line.

B. Series Converter Control System Fig. 2 shows the overall series converter control system. The transmission line real power flow is controlled by injecting a component of the series voltage in quadrature with the UPFC bus voltage . The transmission line reactive power is controlled by modulating the

transmission line side bus voltage reference

. The transmission line side bus voltage is controlled by injecting a component of the series voltage in-phase with the UPFC bus voltage [18].

# III. REAL AND REACTIVE POWER COORDINATION CONTROLLER

A. Real Power Coordination Controller

To understand the design of a real power coordination controller for a UPFC, consider a UPFC connected to a transmission line as shown in Fig. 3. The interaction between the series injected voltage and the transmission line current leads

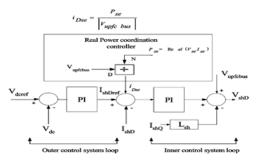

Fig.4. D-axis shunts converter control system with real power coordination controller.

to exchange of real power between the series converter and the transmission line. The real power demand of the series converter causes the dc link capacitor voltage to either increase or decrease depending on the direction of the real power flow from the series converter.

This decrease/increase in dc link capacitor voltage is sensed by the shunt converter controller that controls the dc link capacitor voltage and acts to increase/decrease the shunt converter real power flow to bring the dc link capacitor voltageback to its scheduled value. Alternatively, the real power demand of the series converter is recognized by the shunt controller only the converter bv decrease/increase of the dc link capacitor voltage

Thus, the shunt and the series converter operation are in a way separated from each other. To provide for proper coordination be- tween the shunt and the series converter control system, a feed- back from the series converter is provided to the shunt converter control system. The feedback signal used is the real power demand of the series converter .

The real power demand of the series converter is converted into an equivalent Daxis current for the shunt converter . By doing so, the shunt converter responds immediately to a change in its D-axis current and supplies the necessary series real power converter demand. The equivalent D-axis current is an additional input to the D-axis shunt converter control system as shown in Fig. 4.

Equation (1) shows the relationship between the series converter real power demand and the shunt converter D-axis current

$$i_{Dsc} = \frac{P_{sc}}{|V_{upfc bus}|}$$

. (1)

The real power demands of the series converter is the real part of product of the series converter injected voltage and the transmission line current. Represent the voltage of the bus to which the shunt converter is connected and the equivalent additional D-axis current that should flow through the shunt converter to supply the real power demand of the series converter. As shown in Fig. 4, the equivalent D-axis additional current signal is fed to the inner control system, thereby increasing the effectiveness of the coordination controller.

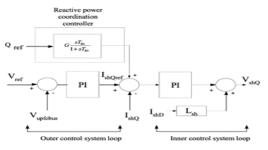

Fig.5. Shunt converter Q-axis controller with reactive power coordination controller

Further, the inner control system loops are fast acting PI controllers and ensure fast supply of the series converter real power demand by the shunt converter.

# B. Reactive Power Coordination Controller

The in-phase component of the series injected voltage which has the same phase as that of the UPFC bus voltage, has considerable effect on the transmission line reactive power and the shunt converter reactive power. Any increase/decrease in the transmission line reactive power due to inphase component of the series injected voltage causes an equal increase/decrease in the shunt converter reactive power [19].

In short, increase/decrease in transmission line reactive power is supplied by the shunt converter. Increase/decrease in the transmission line reactive power also has considerable effect on the UPFC bus voltage. The mechanism by which the request for transmission line reactive power flow is supplied by the shunt converter is as follows. Increase in transmission line reactive power reference causes a decrease in UPFC bus voltage.

Decrease in UPFC bus voltage is sensed by the shunt converter UPFC bus voltage controller which causes the shunt converter to increase its reactive power output to boost the voltage to its reference value.

The increase in shunt converter reactive power output is exactly equal to the increase requested by the transmission line reactive power flow controller (neglecting the series transformer reactive power loss). Similarly, for a decrease in transmission line reactive power, the UPFC bus voltage increases momentarily.

The increase in UPFC bus voltage causes the shunt converter to consume reactive power and bring the UPFC bus voltage back to its reference value [20]. The decrease in the shunt converter reactive power is exactly equal to the decrease in transmission line reactive power flow (neglecting the reactive power absorbed by the series transformer).

In this process, the UPFC bus voltage experiences excessive voltage excursions. To reduce the UPFC bus voltage

excursions, a reactive power flow coordination controller has been designed. The input to the reactive power coordination controller is the transmission line reactive power reference. Fig. 5 shows the shunt converter Q-axis control system with the reactive power coordination controller.

The reactive power coordination controller is not reduced the total harmonic distortion (THD). For this reason introduced five level SPWM based UPFC [21]. The SPWM using for five levels UPFC the reactive power demand is 10MVAR and total harmonic distortion (THD) is 9.01% occurred. So that the five levels SPWM based UPFC have more THD and conduction losses for these causes using SVPWM for a five levels UPFC.

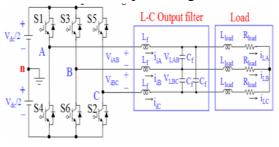

2. Space Vector PWM Principle of Space Vector PWM

The circuit model of a typical threephase voltage source PWM inverter is shown in Fig. 6. S1 to S6 are the six power switches that shape the output, which are controlled by the switching variables a, a, b, b, c and c. When an upper transistor is switched on, i.e., when a, b or c is 1, the corresponding lower transistor is switched off, i.e., the corresponding a, b or c is 0. Therefore, the on and off states of the upper transistors S1, S3 and S5 can be used to determine the output voltage.

Fig. 6 Three-phase voltage source PWM Inverter.

The relationship between the switching variable vector [a, b, c]t and the line-to-line voltage vector [Vab Vbc Vca]t is given by (2.1) in the following:

$$\begin{bmatrix} V_{ab} \\ V_{bc} \\ V_{ca} \end{bmatrix} = V_{dc} \begin{bmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \\ -1 & 0 & 1 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}.$$

(2.1)

Also, the relationship between the switching variable vector [a, b, c]t and the phase voltage vector [Va Vb Vc]t can be expressed below.

$$\begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix} = \frac{V_{dc}}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}.$$

(2.2)

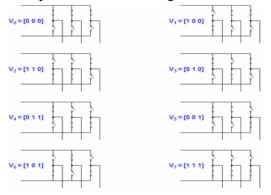

In Fig. 6, there are eight possible combinations of on and off patterns for the three upper power switches. The on and off states of the lower power devices are opposite to the upper one and so are easily determined once the states of the upper power transistors are determined. According to equations (2.1) and (2.2), the eight switching vectors, output line to neutral voltage (phase voltage), and output line-to-line voltages in terms of DC-link Vdc, are given in Table1 and Fig. 7 shows the eight inverter voltage vectors (V0 to V7).

| Voltage        | Switching Vectors |   |   | Line to neutral voltage |      |                 | Line to line voltage |     |    |

|----------------|-------------------|---|---|-------------------------|------|-----------------|----------------------|-----|----|

| Vectors        | a                 | b | c | Van                     | Vba  | V <sub>ci</sub> | Vab                  | Vic | Va |

| V <sub>0</sub> | 0                 | 0 | 0 | 0                       | 0    | 0               | 0                    | 0   | 0  |

| V <sub>1</sub> | 1                 | 0 | 0 | 2/3                     | -1/3 | -1/3            | 1                    | 0   | -1 |

| V <sub>2</sub> | 1                 | 1 | 0 | 1/3                     | 1/3  | -2/3            | 0                    | 1   | -1 |

| V3             | 0                 | 1 | 0 | -1/3                    | 2/3  | -1/3            | -1                   | 1   | 0  |

| V4             | 0                 | 1 | 1 | -2/3                    | 1/3  | 1/3             | -1                   | 0   | 1  |

| V <sub>5</sub> | 0                 | 0 | 1 | -1/3                    | -1/3 | 2/3             | 0                    | -1  | 1  |

| V <sub>6</sub> | 1                 | 0 | 1 | 1/3                     | -2/3 | 1/3             | 1                    | -1  | 0  |

| V <sub>7</sub> | 1                 | 1 | 1 | 0                       | 0    | 0               | 0                    | 0   | 0  |

(Note that the respective voltage should be multiplied by  $V_{dc}$  )

Table.1. Switching vectors, phase voltages and output line to line voltages

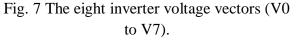

Space Vector PWM (SVPWM) refers to a special switching sequence of the upper three power transistors of a threephase power inverter [22]. It has been shown to generate less harmonic distortion in the output voltages and or currents applied to provide more efficient use of supply voltage compared with sinusoidal modulation technique as shown in Fig. 8.

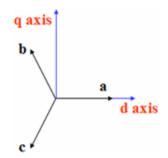

Fig.8 Locus comparison of maximum linear control voltage in Sine PWM and SVPWM To implement the space vector PWM, the voltage equations in the abc reference frame can be transformed into the stationary dq reference frame that consists of the horizontal (d) and vertical (q) axes as depicted in Fig. 9.

Fig.9 The relationship of abc reference frame and stationary dq reference frame.

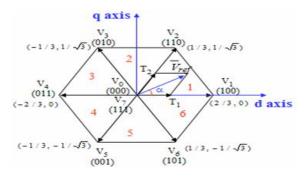

described in Fig. As 9, this transformation is equivalent to an orthogonal projection of [a, b, c]t onto the two-dimensional perpendicular to the vector [1, 1, 1]t (the equivalent d-q plane) in a three-dimensional coordinate system. As a result, six non-zero vectors and two zero vectors are possible. Six nonzero vectors (V1 - V6) shape the axes of a hexagonal as depicted in Fig. 10, and feed electric power to the load.

The angle between any adjacent two non-zero vectors is 60 degrees. Meanwhile, two zero vectors (V0 and V7) are at the origin and apply zero voltage to the load.

The eight vectors are called the basic space vectors and are denoted by V0, V1, V2, V3, V4, V5, V6, and V7. The same transformation can be applied to the desired output voltage to get the desired reference voltage vector Vref in the d-q plane.

The objective of space vector PWM technique is to approximate the reference voltage vector Vref using the eight switching patterns [23]-[25]. One simple

method of approximation is to generate the average output of the inverter in a small period, T to be the same as that of Vref in the same period.

Fig. 10 Basic switching vectors and sectors

Therefore, space vector PWM can be implemented by the following steps:

$\Box$  Step 1. Determine Vd, Vq, Vref, and angle ( $\Box$ )

$\Box$  Step 2. Determine time duration T1, T2, T0

$\Box$  Step 3. Determine the switching time of each transistor (S1 to S6)

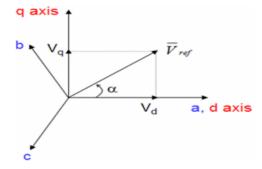

Step 1: Determine Vd, Vq, Vref, and angle From Fig. 11, the Vd, Vq, Vref, and angle can be determined as follows:

$$V_{d} = V_{an} - V_{bn} \cdot \cos 60 - V_{cn} \cdot \cos 60$$

$$= V_{an} - \frac{1}{2} V_{bn} - \frac{1}{2} V_{cn}$$

$$V_{q} = 0 + V_{bn} \cdot \cos 30 - V_{cn} \cdot \cos 30$$

$$= V_{an} + \frac{\sqrt{3}}{2} V_{bn} - \frac{\sqrt{3}}{2} V_{cn}$$

$$\therefore \begin{bmatrix} V_{d} \\ V_{q} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix}$$

$$\therefore |\overline{V}_{ref}| = \sqrt{V_{d}^{2} + V_{q}^{2}}$$

$\therefore \alpha = \tan^{-1} \left( \frac{V_q}{V_d} \right) = \omega t = 2\pi f t, \text{ where } f = \text{fundamental frequency}$

Fig. 11 Voltage Space Vector and its components in (d, q)

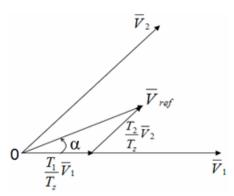

Step 2: Determine time duration T1, T2, T0 from Fig. 12, the switching time duration can be calculated as follows:

Switching time duration at Sector 1

$$\begin{split} & \overset{\mathsf{T}_z}{\underset{0}{\nabla}} \sum_{\mathsf{ref}} = \int_{0}^{\mathsf{T}_1} \overline{\mathsf{V}}_1\mathsf{dt} + \int_{\mathsf{T}_1}^{\mathsf{T}_2} \overline{\mathsf{V}}_2\mathsf{dt} + \int_{\mathsf{T}_1+\mathsf{T}_2}^{\mathsf{T}_2} \overline{\mathsf{V}}_0 \\ & \therefore \mathsf{T}_z \cdot \overline{\mathsf{V}}_{\mathsf{ref}} = (\mathsf{T}_1 \cdot \overline{\mathsf{V}}_1 + \mathsf{T}_2 \cdot \overline{\mathsf{V}}_2) \\ & \Rightarrow \mathsf{T}_z \cdot |\overline{\mathsf{V}}_{\mathsf{ref}}| \cdot \left[ \frac{\cos(\alpha)}{\sin(\alpha)} \right] = \mathsf{T}_1 \cdot \frac{2}{3} \cdot \mathsf{V}_{\mathsf{de}} \cdot \left[ \frac{1}{0} \right] + \mathsf{T}_2 \cdot \frac{2}{3} \cdot \mathsf{V}_{\mathsf{de}} \cdot \left[ \frac{\cos(\pi/3)}{\sin(\pi/3)} \right] \\ & (\mathsf{where}, \ 0 \le \alpha \le 60^\circ) \\ & \therefore \mathsf{T}_1 = \mathsf{T}_z \cdot \alpha \cdot \frac{\sin(\pi/3 - \alpha)}{\sin(\pi/3)} \\ & \therefore \mathsf{T}_2 = \mathsf{T}_z \cdot \alpha \cdot \frac{\sin(\alpha)}{\sin(\pi/3)} \\ & \therefore \mathsf{T}_0 = \mathsf{T}_z - (\mathsf{T}_1 + \mathsf{T}_2), \quad \left( \mathsf{where}, \ \mathsf{T}_z = \frac{1}{\mathsf{f}_z} \ \mathsf{and} \ \mathsf{a} = \frac{|\overline{\mathsf{V}}_{\mathsf{ref}}|}{\frac{2}{3}\mathsf{V}_{\mathsf{de}}} \right) \end{split}$$

□ Switching time duration at any Sector

$$\begin{array}{l} \therefore T_1 = \displaystyle \frac{\sqrt{3} \cdot T_z \cdot |\overline{V}ref|}{V_{dc}} \bigg( \sin \bigg( \displaystyle \frac{\pi}{3} - \alpha + \displaystyle \frac{n-1}{3} \pi \bigg) \bigg) \\ = \displaystyle \frac{\sqrt{3} \cdot T_z \cdot |\overline{V}ref|}{V_{dc}} \bigg( \sin \displaystyle \frac{n}{3} \pi - \alpha \bigg) \\ = \displaystyle \frac{\sqrt{3} \cdot T_z \cdot |\overline{V}ref|}{V_{dc}} \bigg( \sin \displaystyle \frac{n}{3} \pi \cos \alpha - \cos \displaystyle \frac{n}{3} \pi \sin \alpha \bigg) \\ \therefore T_2 = \displaystyle \frac{\sqrt{3} \cdot T_z \cdot |\overline{V}ref|}{V_{dc}} \bigg( \sin \bigg( \alpha - \displaystyle \frac{n-1}{3} \pi \bigg) \bigg) \\ = \displaystyle \frac{\sqrt{3} \cdot T_z |\overline{V}ref|}{V_{dc}} \bigg( -\cos \alpha \cdot \sin \displaystyle \frac{n-1}{3} \pi + \sin \alpha \cdot \cos \displaystyle \frac{n-1}{3} \pi \bigg) \bigg) \\ \therefore T_0 = T_z - T_1 - T_2, \quad \left( \begin{array}{c} \text{where, n = 1 through 6 (that is, Sector1 to 6)} \\ 0 \le \alpha \le 60^{\circ} \end{array} \right) \end{array}$$

Fig. 12 Reference vector as a combination of adjacent vectors at sector 1.

Step 3: Determine the switching time of each transistor (S1 to S6) Fig. 13 shows space vector PWM switching patterns at each sector.

Fig. 13 Space Vector PWM switching patterns at each sector. Based on Fig. 13, the switching time at each sector is summarized

| Sector | Upper Switches (S <sub>1</sub> , S <sub>3</sub> , S <sub>5</sub> )                        | Lower Switches (S <sub>4</sub> , S <sub>6</sub> , S <sub>2</sub> )                                  |

|--------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 1      | $S_{1} = T_{1} + T_{2} + T_{0} / 2$<br>$S_{3} = T_{2} + T_{0} / 2$<br>$S_{5} = T_{0} / 2$ | $\begin{array}{l} S_4 = T_0 / 2 \\ S_6 = T_1 + T_0 / 2 \\ S_2 = T_1 + T_2 + T_0 / 2 \end{array}$    |

| 2      | $S_{1} = T_{1} + T_{0} / 2$<br>$S_{3} = T_{1} + T_{2} + T_{0} / 2$<br>$S_{5} = T_{0} / 2$ | $S_4 = T_2 + T_0 / 2$<br>$S_6 = T_0 / 2$<br>$S_2 = T_1 + T_2 + T_0 / 2$                             |

| 3      | $S_{1} = T_{0} / 2$<br>$S_{3} = T_{1} + T_{2} + T_{0} / 2$<br>$S_{5} = T_{2} + T_{0} / 2$ | $S_4 = T_1 + T_2 + T_0 / 2$<br>$S_6 = T_0 / 2$<br>$S_2 = T_1 + T_0 / 2$                             |

| 4      | $S_{1} = T_{0} / 2$<br>$S_{3} = T_{1} + T_{0} / 2$<br>$S_{5} = T_{1} + T_{2} + T_{0} / 2$ | $\begin{array}{l} S_4 = T_1 + T_2 + T_0 \ /2 \\ S_6 = T_2 + T_0 \ /2 \\ S_2 = T_0 \ /2 \end{array}$ |

| 5      | $S_{1} = T_{2} + T_{0} / 2$<br>$S_{3} = T_{0} / 2$<br>$S_{5} = T_{1} + T_{2} + T_{0} / 2$ | $\begin{array}{l} S_4 = T_1 + T_0 / 2 \\ S_6 = T_1 + T_2 + T_0 / 2 \\ S_2 = T_0 / 2 \end{array}$    |

| 6      | $S_{1} = T_{1} + T_{2} + T_{0} / 2$<br>$S_{3} = T_{0} / 2$<br>$S_{5} = T_{1} + T_{0} / 2$ | $S_4 = T_0 / 2$<br>$S_6 = T_1 + T_2 + T_0 / 2$<br>$S_2 = T_2 + T_0 / 2$                             |

in Table 2, and it will be built in Simulation model to implement SVPWM.

Table.2.SwitchingTimeCalculationatEachSector

### SIMULATION RESULTS

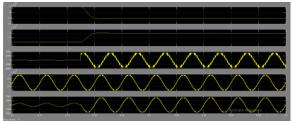

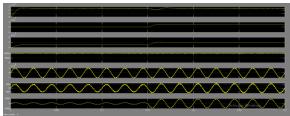

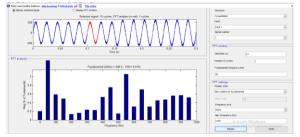

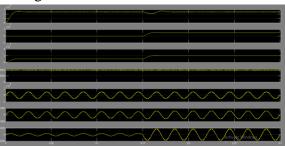

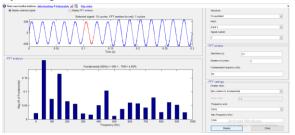

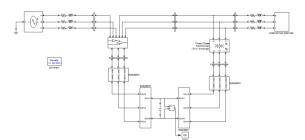

The SPWM using for five levels UPFC the reactive power demand is 10MVAR and total harmonic distortion (THD) is 9.01% occurred shown in fig.14, fig.15 and fig.16. In this paper using SVPWM based five levels UPFC instead of reactive power coordination controller and SPWM. During the simulation, phaseshifted SPWM was used with the carrier and switching frequencies being equal to 1 kHz.

The sending and receiving end bus bar voltages are assumed to be constant, of the same amplitude of 10 kV (peak) and displaced by an angle of 15°. The output voltage of the shunt transformer is 3.75 kV (peak). The series inductance and resistance are 0.1p.u, and 0.01p.u, respectively (10 kV, 30 MVA, 50 Hz base). For the shunt circuit, the inductance and resistance are 0.28p.u, and 0.03p.u, respectively [26].

A relatively large DC capacitor of  $2000\mu$ F is used due to the large power demanded by the series converter at some operating conditions. However, the capacitances for the flying capacitors are set at  $200\mu$ F. This is due to the factor that, for the FC multilevel VSC, the voltage of each flying capacitor is balanced within each switching cycle; therefore, relatively small capacitors can be used.

The DC voltage is well controlled with a small ripple. The simulated results of power flow control by the UPFC system are shown in Fig. 14 for P\*=30 MW, Q\*=0MVAr, in Fig. 15 for P\*=20 MW, Q\*=10MVAr, and Fore there P\*=20 MW, Q\*=10MVAr, respectively. As shown, after the series element of the UPFC is started at the time of 0.15s.

Fig.14 Simulated results of the SPWM based five levels UPFC series converter operation for  $P^*=20MW$ ;  $Q^*=0MVAr$ .

Fig.15 Simulated results of UPFC operation by using flying capacitor converter operation for  $P^*=20MW$ ;  $Q^*=10MVAr$ .

Fig 16 THD values of UPFC operation by using flying capacitor In this paper SVPWM is proposes to reduced reactive power demand 9.5MVAR and total harmonic distortion (THD) 4.85%. Shown in fig.17 and fig.18

Fig.17 Simulated results of UPFC operation by using SVPWM

Fig 18 THD values of UPFC operation by using SVPWM In this paper proposes SVPWM for a five levels UPFC is controlled the reactive power and total harmonic distortion than the other controllers (reactive power coordination control and SPWM). The simulation circuit and simulation control circuits are shown in fig.19 and fig.20.

Fig 19 Simulation circuit of UPFC operation by using SVPWM

Fig 20 Simulation control circuit of UPFC operation by using SVPWM

# CONCLUSION

The possibility of using flying capacitor multilevel SVPWM five level converters for a UPFC application is discussed. The reduction of reactive power and total harmonic distortion (THD) using by SVPWM for a five levels UPFC. For this reason SVPWM is proposes to reduced reactive power demand 9.5MVAR and total harmonic distortion (THD) 4.85%.

A new SVPWM for a five level UPFC has been designed to limit excessive voltage excursions during reactive power transfers. PSCAD-EMTDC simulation results have been presented to show the improvement in the performance of the five levels UPFC control with the proposed reactive power and total harmonic distortion. In this paper proposes SVPWM for a five levels UPFC is controlled the reactive power and total harmonic distortion than the other controllers (reactive power coordination control and SPWM).

# REFERENCES

[1] L. Gyugyi, C. D. Schauder, S. L. Williams, T. R. Reitman, D. R. Torgerson, and A. Edris, "The unified power flow controller: A new approach to power transmission control," IEEE Trans. Power Delivery, vol. 10, pp. 1085–1097, Apr. 1995.

[2] C. D. Schauder, L. Gyugyi, M. R. Lund, D. M. Hamai, T. R. Rietman, D. R. Torgerson, and A. Edris, "Operation of the unified power flow controller (UPFC) under practical constraints," IEEE Trans. Power De-livery, vol. 13, pp. 630–636, Apr. 1998.

[3] K. K. Sen and E. J. Stacey, "UPFC-Unified Power flow controller: Theory, modeling, and applications," IEEE Trans. Power Delivery, vol. 13, pp. 1453–1460, Oct. 1999.

[4] B. A. Renz, A. S. Mehraben, C. Schauder, E. Stacey, L. Kovalsky, L. Gyugyi, and A. Edris, "AEP unified power flow controller performance," IEEE Trans. Power Delivery, vol. 14, pp. 1374–1381, Oct. 1999.

[5] P. K. Dash, S. Mishra, and G. Panda,

"A radial basis function neural network controller for UPFC," IEEE Trans. Power Syst., vol. 15, pp. 1293–1299, Nov. 2000.

[6] HINGORAN 1, N.G., and GYUGYI,

L.: 'Understanding FACTS', (IEEE Press, 2000).

[7] ACHA, E., AGELIDIS, V.G., ANAYALARA, O., and MILLER, T.H.J.: 'Power electronic control in electrical systems', (Newness Powel' Engineering Series, 2002) 'Flexible AC transmission

systems (FACTS) (IEE Power and Energy Series 30, 1999).

[8] GYUGYI. L., SCHAUDER, C.D., WILLIAMS, S.L., RIETMAN, T.R., TORGERSON, D.R., and EDRIS, A.: 'The unified power how controller: A new approach to power transmission control', IEEE Trans. Power Delia. 1995, 10, (2), pp. 1085-1093.

[9] SCHA UDER, C.D., STACEY, E., LUND, M., KERI, M., MEHRABAN, A., EDRIS, A., GYUGYI, L., and KOVALSK\', L.: 'AEP UPFC project: installation, commissioning and operation of the -I- 160 MVA STATCOM (phase I)', IEEE Trans, Power Delia. , 1995, 13, (4), pp. 1530– 1535.

[10] MWI NYIWIWA, B., OOI, B.T., and WOLANSKI, Z.: 'UPFC using multi converter operated by phase-shifted triang1e carrier' SPWM strategy', IEEE Trans. Incl. Appl., 1998, 34, (3), pp. 495-500.

[11] CHEN, Y., and OOI, B.T.: 'Multi modular multilevel rectifier/inverter link with independent reactive power control', IEEE Trans. Power' Delia., 1998, 13, (3), pp. 902—90S.

[12] CHEN, Y., MW INYIWIWA, B., WOLANSKI, Z., and OOI, B.T. 'Unified power flow controller (UPFC) based on chopper stabilized diode-clamped multilevel converters', IEEE Trans Power' Election.,2000, 15, (2), pp. 258-267

[13] TOLBERT, L.M., PENG, F.Z., and HABETLER, T.G.: 'A multi- level converter-based universal power conditioner', IEEE Trans. Incl. Appl., 2000, 36, (2), pp. 596-603 [14] OOI, B.T., and KAZERANI, M.: 'Unified power flow controller based on matrix converter'. Proc. of IEEE PESC'96, 1996, pp. 502-507

[15] MEYNARD, T.A., and FOCH, H.: 'Multi-level conversion: high voltage choppers and voltage-source inverters'. IEEE PESC'92, 1992, pp. 397-403

M EYNARD, T.A. and FOCH, H .: [16] Portent Number 5,737,201, April 7, 1998 UANG, Y., and NWANKPA, C.O.! [17] 'A power-line conditioner based on flyingmultilevel voltage-source capacitor converter with phase-shift SPWM', IEEE Ti ans. Ind. April 2000, 36, (4), pp. 965-971 [18] MAKOMBE, T., and JENKINS, N.: 'Investigation of a unified power flow controller', IEE Proc. Gene Trans/n. Distrib. 1999, 146, (4), pp. 400-408

[19]CAMPOS, A., JOOS, G., ZIOGAS, P.D., rind LINDSAY, J.F, 'Analysis and design of a series voltage compensator for three-phase unbalanced sources', IEEE Trans. Ind. Electron., 1992, 39, (2), pp. 159-167

[20] CAMPOS, A. JOOS, G., ZIOGAS, P.D., and LINDSAY, J.F.: 'Analysis <tm design of a series-connected PWM voltage regulation for single-phase AC sources', IEEE Trans. Ind. Appl., 1996, 32, (6), pp. 1285-1292

[21] YU, Q., ROUJN D, S.D., NORUM, L.E., and UN DELAND, T.M.: 'Dynamic control of a unified power flow controller'. Proc. of IEEE PESC'96, 1996, pp. 508— 514

[22] SCHAU DER, C., and MEHTA, II. 'Vector analysis and control of advanced static VAR compensators', IEE Proc.

B,Elect. Power' Appl., 1993, 140, (4), pp. 295-306

[23] FUJITA, H., WATANABE, Y., and AKAGI, H.: 'Control and analysis of a unified power flow controller', IEEE Tran s. Power Electron, 1999, 14, (6), pp. 1021-1027

[24] FUJITA, H., \VATANABE, Y., rind AKAGI, H.: 'Transient analysis of a unified power flow controller, and its application to design of the DC link capacitor'. IEEE PESC'99, 1999, pp. 62W31

[25] SABER Simulator, Analogy, Inc. USA [26] LAVIEVILLE, J.P., CARRERE, P. and MEYNARD, T.: Patent Number 5,668,711, September 1997.

# AUTHORS

**R. Jayachandra** has obtained his M.tech degree from JNTU Hyderabad. He has more than10 years of teaching experience. He published 4 research papers at National & International level. He is presently a research scholar at JNTUH, Hyderabad, Telangana. He is working in the area of FACTS Controllers & Algorithms.

E-mail: saimedha.J@gmail.com

Prof. G. Tulasi Ram Das has obtained his M.E from Osmania University and Ph.D from IIT Madras. He has more than 30 years of teaching experience. He has published 151 research papers at National and International level. His research area is Industrial Drives, FACTs devices. Telangana, India.

E-mail: das123tulasiram@gmail.com.