# Access of Delay And Power Consumption using Differentfull Adder S in 180nm and 45nm Technology

Raveendrababu Pakala, Associate Professor, Department of ECE, CMR College of Engineering & Technology, Hyderabad, India.(Email: praveendrababu@cmrcet.com)

Dr. M. Nagaraju Naik, Associate Professor, Department of ECE, CMR College of Engineering & Technology, Hyderabad, India.(Email: nagarajunaik1976@cmrcet.org).

Article Info Volume 82 Page Number: 3157 - 3162 Publication Issue: January-February 2020

Article History

Article Received: 14 March 2019 Revised: 27 May 2019 Accepted: 16 October 2019 Publication: 19 January 2020

#### Abstract

Abstract: Adders are the key structure disillusions in forefront PC systems. Math errands are ordinarily used in most novel PC system. Choice is a major math improvement and is the base for number juggling attempts, for instance, increment and the focal snake cell can be changed to fill in as subtracted by including another Xor entryway and can be used for division. Thusly, 1\_bit full snake cell is the most colossal and central square of a number juggling unit of structure. Beginning now and into the not too far-removed to improve the introduction of the incited PC structure one must improve the central 1\_bit full snake cell. There is enterprisingly a trade – off among speed and power scattering in VLSI structure. In this undertaking, various sorts of full snake plans are performed.3T Xor with mux reason is used in 8 transistor fulladder,4T Xor with mux methodology for tolerating is used in 10transistor full adder,12 transistor full snake is composed using multiplexers &14 transistor is formed using 6T Xnor . Assorted strategy are used for low control in full adders. Evaluation relies upon some reenactment parameters like number of transistors, power, deferral and different sorts of progress (gpdk 45nm &180nm sorts of headway) at different supply voltage.

Keywords: Consumption, pc structure, entryway, snakecell.

## I. INTRODUCTION

Improvements are real figuring assignments. It is fundamentally used in pile of VLSI structure, for instance, chip and application unequivocal DSP plan. Furthermore its major endeavor is including two numbers, it is used in various other unsurprising works out. for instance, subtraction, multiplication, address estimation, etc. Building low control VLSI structure has ascended as target. Execution objective because of the burning improvement in adaptable correspondence and figuring. The upgrades in battery improvement have not happened as quick as the advances in electronic contraptions. So the originators are made with on and on; fast, high throughput and all the while, low control use as could be standard the condition being what it is. In various PCs and various sorts of processors, adders are used in the number juggling framework for hypothesis units, yet in like way in various bits of the processor, where they are used to pick addresses, table records, and proportional exercises. Notwithstanding the way where that adders can be passed on for some numerical depictions, for instance, twofold coded decimal, the recognizable adders obliterate most framed numbers. In conditions where two's update or ones' improvement is being used to address negative numbers, it is minor to change a snake into a snake sub tractor. Other meandered number outlines require a plainly flexible snake. Full snake is one of the most central bits of a processor, as it is used in the Arithmetic Logic Unit (ALU), in the skimming point unit and for area age if there ought to be an event of store or memory get to. A few refinements has been made concerning its structure since its

development. The central inspiration driving those progressions is to decrease the degree of transistors to be used to play out the required reason, ruin the power use and extension the speed of improvement. One of the genuine central fixations in diminishing the degree of transistors is to put more contraptions on a single silicon chip there by reducing the determined district. In the tireless days the use of preservationist electronic contraptions like cell devices. workstations has been widened exponentially. The central fundamental of these versatile contraptions is decreased power use, little zone and red hot of advancement. Consequently, the low control use close least surrender and area fundamentals is one of basic methodology thought for IC modelers in organizing unessential electronic contraptions and various shocking mechanical social affair circuits..

## II. DESIGN OF PROPOSED FULL ADDER CIRCUITS

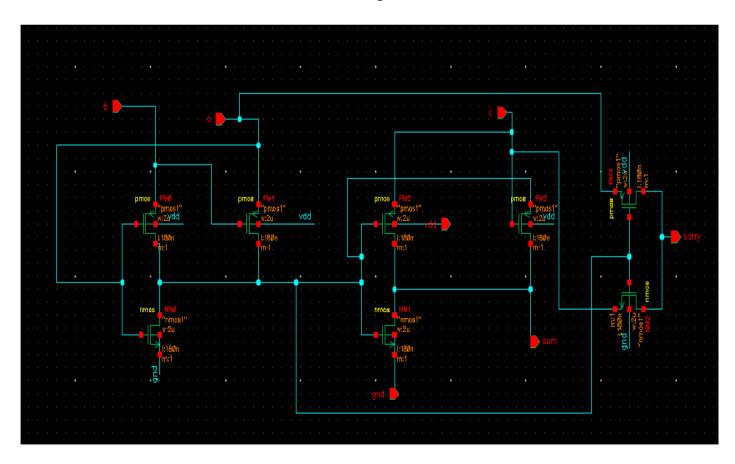

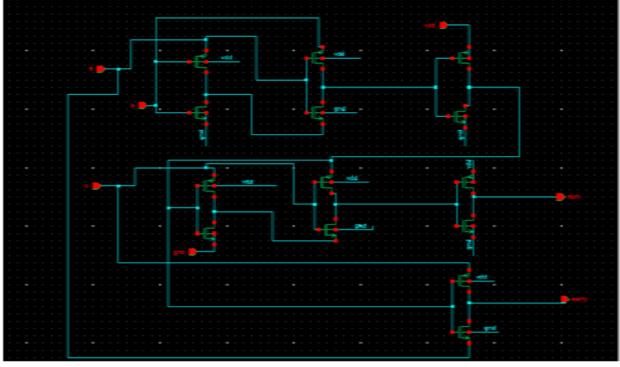

#### PROPOSED8TRANSISTORFULLADDER

The XOR entryway is the huge structure square of the full snake circuit. The introduction of the full snake can be improved by redesiging the presentation of the XOR door. The proposed new procedure of XOR structure for discovering area using three transistors is showed up in Figure. The game-plan relies upon changed CMOS inverter and PMOS pass transistor support. Adequately when the data Y is at technique for hypothesis one, the inverter on past what many would consider possible as a standard CMOS inverter. As necessities be the vield is the improvement of data X. Obviously when the information Y is at reason zero, the CMOS inverter yield is at high impedance. Regardless, the PMOS pass transistor is turned ON and the yield gets a relative affirmation see as data X.

fig:2.1: Schematic of 8T full adder

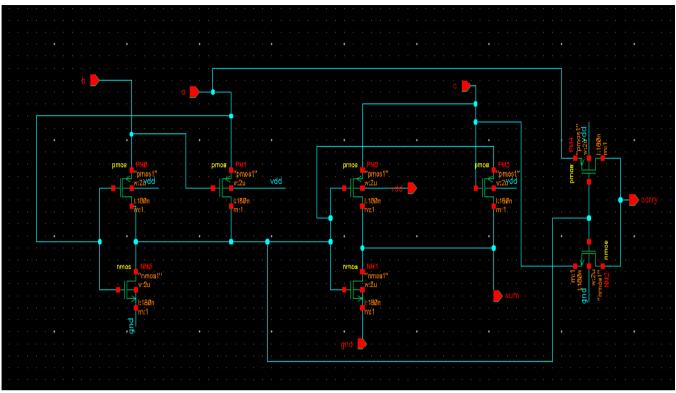

#### PROPOSED10TRANSISTOR FULL ADDER:

The proposed 10T full snake is in like manner called as SERF (Static Energy Recovery Full snake). The Static Energy Recovery Full Adder (SERF) uses only 10 transistors to execute the full snake work.

The strategy was mixed by the XNOR door full snake structure. The structure of SERF is given in schematic underneath

fig:2.2: Schematic of 10T full adder

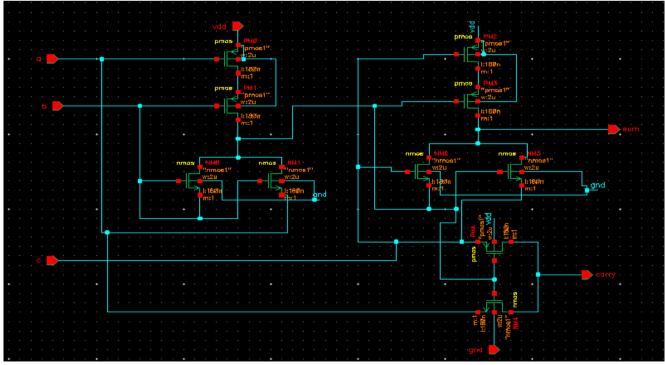

### PROPOSED 12 TRANSISTOR FULL ADDER

Pass transistor hindrance is used to improve the presentation of math and framework for speculation circuits. This system for nature can be used to diminish the power dispersing in the structure and to build up the speed of improvement of the processor. By using pass transistor system for thinking the degree of transistor check can in like manner be diminished when showed up differently in association with static CMOS technique in understanding the stunning structures. Right when the degree of transistor are diminished the zone of the chip decreases in parallel.

fig:2.3: Schematic of 12T full adder

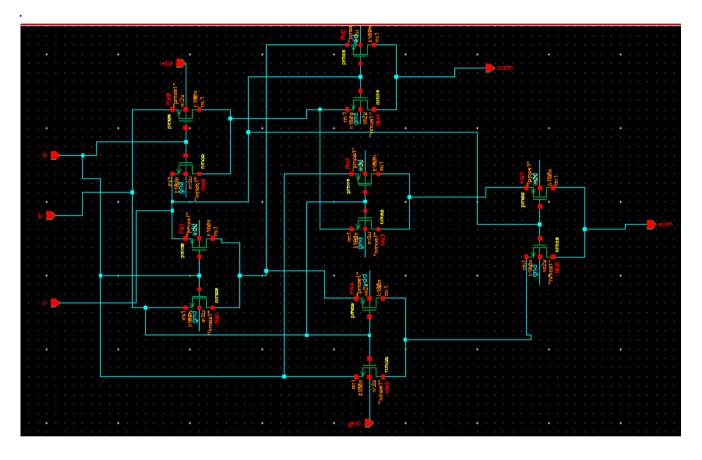

#### PROPOSE 14 TRANSISTORS FULL ADDER

The 14T snake cell requires only 14 transistors to comprehend the snake work. It makes the better achieve edge event, speed and impact by surrendering four extra transistors for each snake cell. The proposed snake execute the Sum using XNOR-XNOR and Cout using PMOS – NMOS We can in like way work to pass on Cout using NMOS-NMOS and PMOS-PMOS. Regardless, the deferral and effect dispersal of PMOS-NMOS is better than other two sorts of making Cout .The proposed XNOR territory is made by putting inverter at the yield of the XOR segment in order to improve the edge disaster issue, which exists in the SERF snake. Out of the three structures, PMOS-NMOS

basedCout gives the better see effect, speed and edge hardship issue.

Fig: 2.4: Schematic of 14T Full adder

## **III. RESULTS**

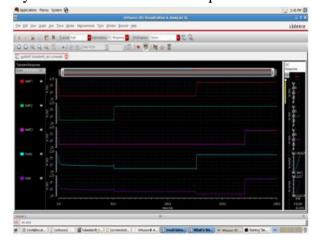

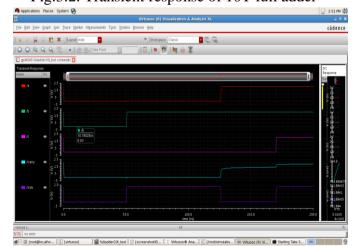

In this project different types of 1-bit Full adders with 8,10,12 & 14 Transistors are designed using 180nm and 45nm technology and the results i.e. transient response of each designed is discussed in the Fig.3.1 to 3.4 and some observed some variations in the Time delay and Power consumption are the listed in Table 3.1. The results of this project indicate that there is a trade off between power consumption and Time delay. In 8T design the time delay is more but it consumes less power and 14T delay is less and consumes more power.

Fig.3.1. Transient response of 8Tfulladder

Fig.3.2. Transient response of 10T full adder

Fig.3.3. Transient response of 12T full adder

#### **IV. CONCLUSIONS**

In this thesis various full adders are designed and verified the simulation results.. Delay and power consumption of different full adders (8 transistor (8T), 10 transistor (10T), 12 transistor (12T) & 14 transistor (14T)) in both 180nm & 45nm technology are compared.

#### **V. REFERENCES**

- [1] Jagadguru Swami Sri Bharati Krishna TirthjiMaharaja,"Vedic Mathematics", MotilalBanarsidas, Varanasi, India, 1986.

- [2] Harpreet Singh Dhillon and AbhijitMitra, "A Reduced- Bit Multiplication Algorithm for Digital Arithmetics", International Journal of Computational and Mathematical Sciences 2;2 ©www.waset.org Spring 2008.

- [3] ShripadKulkarni, "Discrete Fourier Transform (DFT) by using Vedic Mathematics", report, vedicmathsindia.blogspot.com, 2007.

- [4] HimanshuThapliyal, SaurabhKotiyal and M. B Srinivas, "Design and Analysis of A NovelParallel Square and Cube Architecture Based On Ancient Indian Vedic Mathematics", Centrefor VLSI and Embedded System Technologies, International Institute of InformationTechnology, Hyderabad, 500019, India, 2005 IEEE

- [5] ShamimAkhter, "VHDL Implementation of Fast NXN Multiplier Based on Vedic Mathematics", Jaypee Institute of Information Technology University, Noida, 201307 UP, INDIA, 2007 IEEE

- [6] HimanshuThapliyal and M.B Srinivas, "An Efficient Method of Elliptic CurveEncryption Using Ancient Indian Vedic Mathematics", IEEE, 2005.

- [7] El hadjyoussefwajih, ZeghidMedien, Machhout Mohsen,

BouallegueBelgacem, TourkiRached, "Efficient Hardware Architecture of Recursive Karatsuba-OfmanMultiplier", 2008 International Conference on Design & Technology of IntegratedSystems in Nanoscale Era

- [8] Abhijeet Kumar, Dilip Kumar, Siddhi, "Hardware Implementation of 16\*16 bit Multiplierand Square using Vedic Mathematics", Design Engineer, CDAC, Mohali.

- [9] HimanshuThapliyal and Hamid R. Arabnia, "A Time-Area- Power Efficient Multiplier andSquare Architecture Based On Ancient Indian Vedic Mathematics", Department of ComputerScience, The University of Georgia, 415 Graduate Studies Research Center Athens, Georgia30602-7404, U.S.A.

- [10]"Spartan-3E FPGA Starter Kit Board User Guide",<br/>UG230 (v1.1)June20,20