# Strong Multiplier Structure Execution on FPGA With Variable Latency

Ms. V. Remya<sup>1</sup>, Ms. S. Rajalakshmi<sup>2</sup>, Mr. G. C. Jagan<sup>3</sup>, Dr. J. Brittopari<sup>4</sup> <sup>1</sup>Assistant Professor, Department of ECE, SriSairam EngineeringCollege, Chennai <sup>2</sup>Assistant Professor, Department of ECE, SriSairam EngineeringCollege, Chennai <sup>3</sup>Assistant Professor, Department of ECE, Jeppiaar Engineering College, Chennai <sup>4</sup>Assistant Professor, Department of ECE, Presidency University,Bangalore

Article Info Volume 82 Page Number: 2844 - 2848 Publication Issue: January-February 2020

#### Abstract:

The most essential number shuffling commonsense units are Digital Multipliers. The general execution of such structures rely upon the multiplier throughput. In the meantime, if negative bias (Vgs = -Vdd) is applied to the pMOS transistor, the negative bias temperature uncertainty sway happens which makes the edge potential of the pMOS transistor to grow, and decreasing the speed of the multiplier. In the same manner, positive bias temperature uncertainty happens if a positive bias voltage is applied to the nMOS transistor. In like way, it is crucial to structure solid world class multipliers. A creating cautious multiplier structure with novel adaptive hold logic (AHL) circuit is proposed in this work. In addition, the proposed multiplier configuration will be relevant to portion or area bypassing multiplier. The exploratory outcomes show that our proposed structure with  $16 \times 16$  zone bypassing multipliers or with  $16 \times 16$  zone bypassing multipliers. The adaptive hold logic circuit uses a developing careful trustworthy multiplier plan in the designing proposed. Method named Variable-inactivity will be utilized by the multiplier structure. For efficient working, even with impact of negative bias temperature uncertainty and positive bias temperature uncertainty impacts, the Adaptive Hold Logic circuit is utilized. The utilization of this design incorporates Fourier transform, discrete cosine transform and also on digital filters. The Adaptive hold Logic can be actualized in FPGA mimicked in ModelSim and Xilinx programming utilizing Verilog HDL (VHDL). It has a preferred position of limiting the degradation in performance and lessening delay of the multiplier. For future improvement, a RS-Encoder based structure can be presented in the multiplier.

Article History Article Received: 14 March 2019 Revised: 27 May 2019 Accepted: 16 October 2019 Publication: 18 January 2020

Keywords: Variable Latency, AHL, VerilogHDL, FPGA

#### I. INTRODUCTION

In Digital Signal Processing applications, for example, fourier transform, DCT (Discrete Cosine transform) and computerized shifting, multipliers assume a significant job. The structure of these multipliers are mind boggling in nature circuits and it should be worked at a increased clock rate. The postponement of the multiplier ought to be limited to improve the efficiency. A significant issue with the nanometer advances is the debasement in dependability of the circuit. Bias Temperature

Uncertainity is one of the significant explanation behind execution t in nano scale circuits.

Negative Bias Temperature Uncertainity issue will be looked by PMOS transistors working with negative entryway to source voltage. The expansion in limit voltage Vth increments happens with time, due to Negative Bias Temperature Uncertainity impact. On account of increment in edge voltage with time there will be decrease in execution of the framework after some time. Comparable sort of impact will be looked by NMOS transistor is

Positive Bias Temperature Uncertainity. Timing infringement in multiplier is brought about by Negative Bias Temperature Uncertainity and Positive Bias Temperature Uncertainity impacts thus the entire framework may get influenced. Thus, a solid multiplier configuration is basic to acquire agreeable execution. For the best possible presentation of the framework, basic way delay is utilized as framework check cycle in conventional circuits and it might cause critical planning wastage. The planning wastage in customary circuits can be limited by fusing variable latency structure in the framework. In factor inertness structure, the circuit can be implemented in two different ways: in shorter way and in longer way. The activity can be accurately executed by shorter way in one cycle and longer way in more than one cycle.

For diminishing Bias Temperature Uncertainity variable inertness multiplier impact, a solid configuration is proposed in this paper. Adaptive Hold Logic circuit guarantees appropriate execution by altering cycle periods. An Error detection and Correction Pulsed Latch (ECPL) circuit is utilized for recognizing timing infringement.

Related works and the proposed techniques were dealt separately in Part II and III. Part IV deals with the examination of results. Part V concludes the work.

#### **II. EXISTING METHOD**

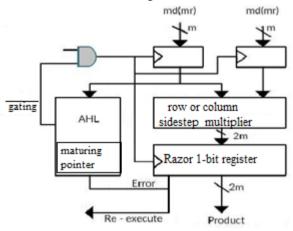

Current framework deals with the usage of row or column sidestep multiplier alongside Adaptive Hold Logic circuit to diminish maturing impact as appeared in fig 1. Timing infringement are recognized utilizing razor single bit register before the appearance of the data input coming immediately. In ordinarily utilized multiplication strategy, addition and shifting of data is done. Column sidestep multiplier is an altered type of typical cluster multiplier. In cluster multiplier every full adders are dynamic regardless the information.

The behaviour of row or column sidestep multiplier depends upon data input. In column sidestep multiplier, the fragmentary product might be zero, if there is zero in atleast one bit. Thusly, it deactivates the referring to section of adders and steer clear of the past result to subsequent stage. So it utilizes less strength and give short of movement when appeared differently in relation to show multiplier.

Figure. 1. Existing Architecture

A multiplexer is utilized to accomplish the bypassing activity. The current design comprises of a row or column sidestep multiplier alongside AHL and razor single bit register. Utilization of zone will be more for section sidestep multipliers. This is on the grounds that row or column sidestep multipliers uses huge count of multiplexers, full adders and tristate buffers. This outcomes in more postponement. Subsequently at the yield of the razor flip lemon, a postponed output is gotten.

In this paper, another circuit for timing mistake location and adjustment is proposed. This methodology is portrayed by ease, less power utilization and decreased plan multifaceted nature as for prior structure conspires in the writing.

#### **III. PROPOSED METHOD**

Determining the appropriate multiplier for advanced circuits is very essential. Subsequent to contrasting the aftereffects of different types of algorithms used by multipliers such as cluster algorithm, segment sidestep algorithm, booth

algorithm and vedic algorithm, it is seen that booth algorithm is generally proficient. Modified Booth algorithm performs both expansion and subtraction and treats both positive and negative operands consistently. The proposed architecture comprises of three principle squares. A multiplier employing radix-4 booth algorithm, an (ECPL) circuit, which is used to identify timing infringement and an AHL circuit, which is to distinguish either the multiplier is following a single or double cycle activity.

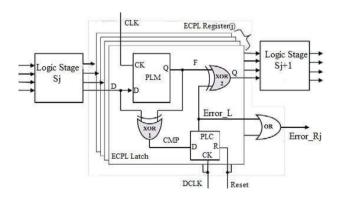

#### A. Error Correction Pulsed Latch (ECPL)

The latch which is synchronized with a pulse and which holds verv short the characteristics of either single bit register or latch. The structure of Error Correction Pulsed Latch circuit is appeared in figure. 2. Two XOR logic gates, an additional correction latch named PLC and a principle latch named PLM are utilized for the planning ECPL circuit. A pulsed clock signal operates the PLM while a deferred clock signal operates the PLC. Offbeat reset is utilized in PLC. The first XOR gate, XOR1 will recognize whether there is any blunder by contrasting the source of PLM and the yield of PLM.

Figure. 2. ECPL circuit

In the event that there is a planning infringement, at that point the yield of the XOR will be in ON state else, it is in OFF state. PLC receives this yield from the XOR gate. To obtain the best possible operation of ECPL circuit, the PLC ought to be brought to OFF state at first. This correlation result was transferred to the PLC circuit utilizing a deferred clock beat. Within the sight of timing infringement Error L signal changes to ON state and it is given to second XOR gate, XOR2. XOR2 alters the bogus incentive at the yield of main Latch by toggling the output. On the off chance that there is no planning infringement, at that point the yield of the Error L signal goes to OFF state and the XOR2 transfers the yield all things considered.

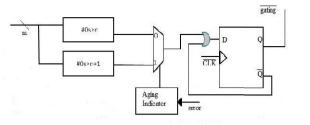

### B. Adaptive HoldLogic

To break down the clock time of the circuit, Adaptive Hold Logic (AHL) is utilized. Figure. 3 illustrates the representation of Adaptive Hold Logic circuit. Two decision making squares, one Multiplexer, one D type single bit register and an maturing pointer are viewed as the significant squares of AHL. The maturing pointer can be a counter. Timing infringement will be brought about by shorter cycle period though timing wastage will be brought about by longer cycle period. So the cycle time frame will be controlled by AHL circuit contingent upon the info signal.

To start with, odds of timing infringement are irrelevant. Subsequently, a OFF is gotten at the yield of maturing pointer and it will choose the principal decision making square. In the event that there is any planning infringement because of maturing, at that point the ECPL will identify this planning infringement and it is given to maturing pointer. On the off chance that mistake surpasses a predefined edge, it implies the maturing impact is huge and the maturing pointer will choose the subsequent passing judgment on square. For this situation, the framework will execute just more modest number of examples in a single cycle.

Figure.3. Adaptive Hold Logic (AHL)

On the off chance that it is a one cycle design, at that point the yield of the multiplexer will be ON and it is given to D type single bit register. At that point  $\overline{gating}$  sign will be moved to ON state and it directs the information flip-failures to lock new information in the following clock cycle. On the off chance that the info signal is two cycle design, at that point the yield of the multiplexer will be OFF state. At that point the clock sign for the information flip will be crippled as the  $\overline{gating}$  sign will be moved to OFF state. Hence, the info single bit register can't hook new information in the following clock.

#### IV. RESULTS ANDDSCUSSION

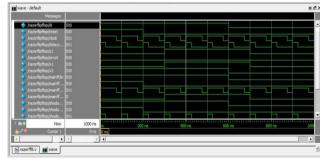

With the assistance of Xilinx ISE, the results were obtained. EDC latch, Razor register and Error Correction Pulsed Latch are the three of timing infringement Error circuits reproduced in xilinx.

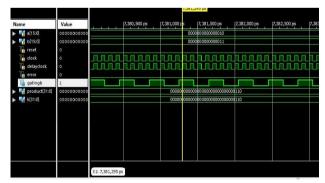

Figure.4. Error Correction Pulsed Latch

Table I demonstrates the examination after effect of these circuits concerning delay. Table I demonstrates that Error Correction Pulsed Latch has minimized delay. Figure. 4 showcase the output of 8-bit ECPL circuit.

Table I: Ccomparision of different multipliers on basis ofarea

| DESCRIPTION   | AREA ANASLYSIS |

|---------------|----------------|

| COLUMN BYPASS | 682 LUTs       |

| TECHNIQUE     |                |

| BOOTH         | 390 LUTs       |

| MULTIPLIER    |                |

| DADDA         | 340 LUTs       |

| MULTIPLIER    |                |

| VEDIC         | 541 LUTs       |

| MULTIPLIER    |                |

The correlation consequence different of multipliers with various piece size were showcased in table II. Among the various multiplier structure booth algorithm gives better execution. The reproduction results show that utilizing booth algorithm postponement and region can be decreased and it additionally confirms that the normal fanout is minimized.

The results of existing 32-bit column sidestep multiplier excluding blunder is appeared in figure. 5 individually.

Figure.5. Column side step Multiplier

Numerous blunders are infused by embedding a XOR gate before the contribution of the PLM obstruct in each ECPL latch.

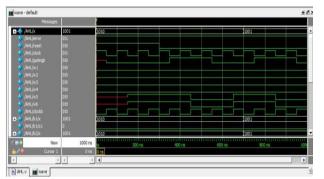

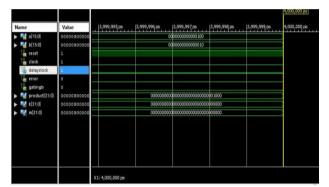

Results of Adaptive hold Logic is showcased in figure6. Output of proposed booth multiplier is appeared in figure. 7.

Figure.6. Adaptive Hold Logic

Figure.7. Proposed Booth Multiplication Technique

| Table II: Comparison of different multipliers on |  |

|--------------------------------------------------|--|

| basis of timing report                           |  |

| DESCRIPTION   | TIMING REPOERT |

|---------------|----------------|

| COLUMN BYPASS | 85.803ns       |

| TECHNIQUE     |                |

| воотн         | 25.26ns        |

| MULTIPLIER    |                |

| DADDA         | 20.516ns       |

| MULTIPLIER    |                |

| VEDIC         | 1115.811ns     |

| MULTIPLIER    |                |

circuit. The multiplier is effectively implemented utilizing Xilinx ISE. By utilizing ECPL circuit the delay can be decreased in output and it guarantee legitimate working of the multiplier. The data input in each clock cycle is investigated by AHL circuit and by choosing legitimate clock it can abstain from timing infringement. Booth multiplier gives great when with execution contrasted different multipliers. The area occupied by the Booth algorithm is less when contrasted with row or column sidestep multiplier. Aside from this, it has minimal delay and greatest throughput.

## VI. REFERENCES

[1]K.C. Wu and D. Marculescu, "Aging-aware timing analysis and optimization considering path sensitization," in Proc. DATE, 2011, pp. 1-6.

[2]H.I. Yang, S.C. Yang, W. Hwang, and C.T. Chuang, "Impacts of NBTI/PBTI on timing control circuits and degradation tolerant design in nanoscale CMOS SRAM," IEEE Trans. Circuit Syst., vol. 58, no. 6, pp. 1239–1251, Jun. 2011.

[3]Y. Liu, T. Zhang, and K. K. Parhi, "Computation error analysis in Digital signal processing systems with over scaled supply voltage", IEEE Apr. 2010.

[4]Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block IEEE Trans., March 2016.

[5]M. C. Wen, S. J. Wang, and Y. N. Lin, Low power parallel multiplier with column bypassing, in Proc. IEEE ISCAS, May 2005, pp. 1638-1641.

[6]R. Wang, K. Martin, D. Johns, and G. Burra, "A 3.3 mW 12 MS/s 10 bit pipelined ADC in 90 nm digital CMOS," in IEEE ISSCC 2005 Dig. Tech. Papers, Feb. 2005, pp. 278–279

## V. CONCLUSION

A maturing multiplier is planned with Adaptive Hold Logic and Error Correction Pulsed Latch